Other Parts Discussed in Thread: C2000WARE

Hi,

I just wanted to know if there is an example included in the C2000 ware that shows a Request-Response handshake mechanism or something similar between the two CPUs.

Thanks,

Rashmitha

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hi,

I just wanted to know if there is an example included in the C2000 ware that shows a Request-Response handshake mechanism or something similar between the two CPUs.

Thanks,

Rashmitha

Hi Santosh,

In cpu01_to_cpu02_ipcdrivers_cpu01.c, the MSG RAM used is CPU02TOCPU01_PASSMSG 0x0003FBF4.

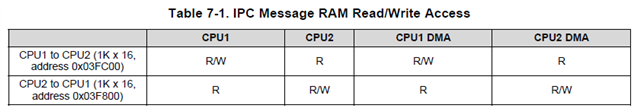

As per the manual, CPU2 has R/W access and CPU1 has only R access to this RAM

But the example implements IPCLtoRDataWrite and IPCLtoRBlockWrite to this RAM (i.e. CPU01 is writing to 0x0003FBF4).

Could you please explain this?

Hi Rashmitha,

Please look into the implementation of the driver functionIPCLtoRDataWrite. Actually, it send the address and value. Then actual write is done by CPU2.

You can also refer to IPC driver user's guide. It is included in C2000Ware SDK install, and it is located here.

C:/ti/c2000/C2000Ware_3_04_00_00/device_support/f2837xd/docs/F2837xD_IPC_Driver_UG.pdf

Hi Santosh

I looked into the code and doc too.

The user guide says "This function will allow the local CPU system to write a block of data to the remote CPU system starting from the location specified by the ulAddress parameter. Prior to calling this function, the local CPU system code should place the data to write in shared memory starting at /e ulShareAddress."

Here Local is CPU1 and Remote is CPU2, and ulAddress being passed is pulMsgRam which is 0x0003FBF4. ulShareAddress is Global shared RAM address.

So in cpu01_to_cpu02_ipcdrivers, as per the guide if IPCLtoRDataWrite is called it should be CPU1 doing the write to the shared memory, isn't it?

Rashmitha,

If you have a board (F28379D controlCARD or Launchpad), I will suggest you to build the code and run the codes on target.

On CPU1, it populated a structure, which has address and value, then send ipc command. On CPU2, it wakes IPC ISR, then it reads the address and writes the value. So actual write happens on CPU2

Santosh,

Thank you. I understand.

So if I want to build an application using this driver where in some data read by CPU1 needs to be passed to CPU2 using IPC,

I should be using cpu01_to_cpu02_ipcdrivers and MSG RAM-> CPU02TOCPU01_PASSMSG as 0x0003FBF4

I just need to be aware that even though it is a data pass from CPU1 to CPU2, data writing is actually done by CPU2 (the Remote CPU) & not the source CPU.

Is my understanding correct?

Thanks,

Rashmitha

Rashmitha,

That is correct. The ipc driver example walks through different ways to communicate between the CPUs.

Hi Santosh,

Could you suggest the best option to run through the code on both cores together/simultaneously?

Because when I pause manually at certain places on one CPU I am not able to go through the the entire control flow and I am unable to find at which places CPU2 in coming into the flow.

Rashmitha,

You can set the breakpoint on IPC/ISR for cpu1 and cpu2, then follow the code from there.

in cpu1 file : __interrupt void CPU02toCPU01IPC0IntHandler (void)

for cpu2 file : __interrupt void CPU01toCPU02IPC0IntHandler (void)

Hi Santosh,

Thank you for the solution.

I have another question regarding the buffers used for Block WRITE/READ

On CPU1 we have

uint16_t usCPU01Buffer[256]; (Which is initialized with a data block of size 256 on CPU1)

On CPU2 we have

uint16_t usCPU02Buffer[256]; (The Address of this is 0x0000 A9C0)

And then this address is assigned to pulMsgRam like shown below

pulMsgRam[2] = (uint32_t)&usCPU02Buffer[0];

When I load the code and do stepping I find that both usCPU01Buffer and usCPU02Buffer are at 0xA9C0

and in the memory browser A9C0 is shown as usCPU01Buffer

Question:

Is there a part of the driver that links both of these buffers to same address?

Since both are declared and defined separately shouldn't they be at 2 different RAM locations?

Rashmitha,

I see you have created another thread on this topic. So I will close this thread and work on that thread.