Part Number: TMS320F28069

Other Parts Discussed in Thread: C2000WARE

Hi Expert,

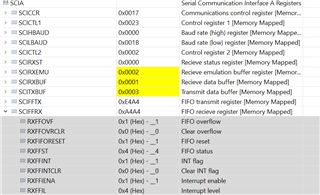

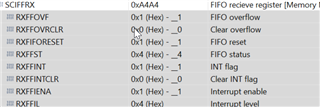

My customer are facing an issue that SCI receive overflow and SciaRegs.SCIFFRX.bit.RXFFOVF is 1, but sometimes did not go to the interrupt.

as the TRM mention, when SCI receive overflow occur, there should be able to go to the interrupt.

I did the test with control card and modified the code from c2000ware as below, when set overflow_test=1 in ccs windows, there will not read data and will cause receive data overflow:

in sciaRxFifoIsr also reset the SCI according to flag SciaRegs.SCIFFRX.bit.RXFFOVF.

sciaRxFifoIsr(void)

{

Uint16 i;

if(SciaRegs.SCIFFRX.bit.RXFFOVF ==1)

{

overflow_test = 0;

SciaRegs.SCICTL1.all = 0x0023;

SciaRegs.SCIFFTX.bit.TXFIFOXRESET = 1;

SciaRegs.SCIFFRX.bit.RXFIFORESET = 1;

overflow_count++;

}

if(overflow_test ==0)

{

for(i=0;i<1;i++)

rdataA[i]=SciaRegs.SCIRXBUF.all; // Read data

}

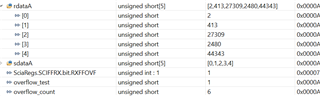

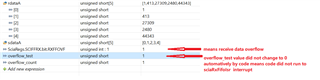

Just set overflow_test to 1 and see the result, did the test several times will find that, SciaRegs.SCIFFRX.bit.RXFFOVF is 1, but did not enter the interrupt sciaRxFifoIsr again.

Anything wrong here? why would have case that SciaRegs.SCIFFRX.bit.RXFFOVF is 1 but the code did not run to sciaRxFifoIsr ?