Hi!

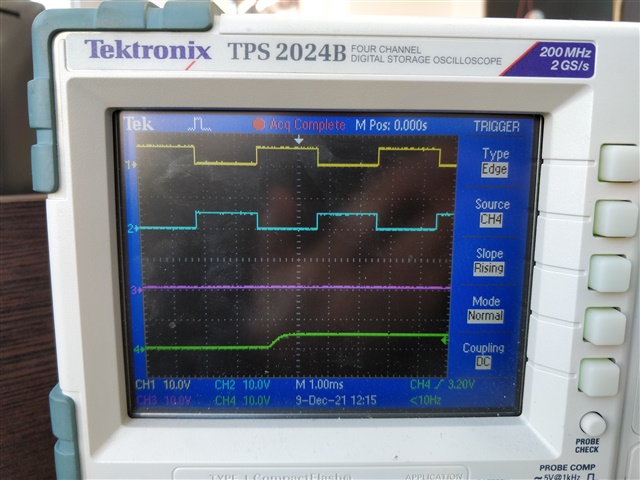

I ran into a problem when using DCAEVT1 and DCBEVT1 events.

I want to setup ePWM module to complementary operation mode with dead time.

Also l want to be able to block (set to HIZ state) either channel A switch or channel B switch by software independently.

According to the documentation, DCAEVT1 and DCBEVT1 events can be used for this purpose.

I set up ePWM module this way:

EPwm7Regs.TZCTL.bit.DCAEVT1 = 0;

EPwm7Regs.TZCTL.bit.DCBEVT1 = 0;

Switches blocking/deblocking is carried out this way:

EPwm7Regs.TZFRC.bit.DCAEVT1 = 1;

EPwm7Regs.TZCLR.bit.DCAEVT1 = 1;

EPwm7Regs.TZFRC.bit.DCBEVT1 = 1;

EPwm7Regs.TZCLR.bit.DCBEVT1 = 1;

Deadband module is set up this way:

EPwm7Regs.DBCTL.bit.IN_MODE = DBA_ALL; //0x0

EPwm7Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC; //0x2

EPwm7Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE; //0x3

DCAEVT1 and DCBEVT1 flags in EPwm7Regs.TZFLG are set and cleared properly. But there is no reaction in ePWM outputs. Both A and B channels keep operating despite the flags. I could not find any other settings in the documentation that are necessary for these events to work. Can you help me with this problem?