Other Parts Discussed in Thread: C2000WARE

Dear TI-Support team,

in my bootloader I like to start the Co-CPUs CPU2 and the CM core with the boot option `IPC Message Copy to RAM Boot`. I thought after a successfull boot I have to read some data at the associated RAM locations.

For CPU2 the code has to be copied to M1-RAM starting at address 0x400 and for CM the code has to be copied to S0-RAM starting at address 0x20000800. I thought after a successfull boot I can read some data of these locations. But unfortunately I just read 0000 at these locations after connecting with the debugger and reading the memory.

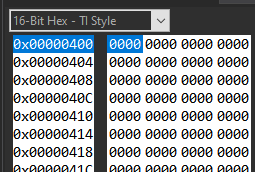

CPU2 memory browser content at address 0x400

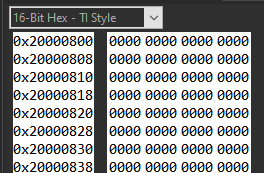

CM memory browser content at address 0x20000800

This is my Bootupconfiguration:

/// Start Adresses of the Sectors, which must be copied during MSGRAM BOOT Option

/// for CPU2 and CM. Sectors with this start Adress shall not be transfered during

/// the dynamic program load service.

#define MSGRAM_BOOT_SECTOR_CPU2 0x00000400

#define MSGRAM_BOOT_SECTOR_CM 0x20000800

/// IPC BOOTMODE Register values, for booting from ipc msgram copy boot option

/// For more details see sprui0 (tech. ref. guide) kap. 5.7.2.2 `IPCBOOTMODE Details`

#define IPC_BOOTMODE_REG_CONTENT_CPU2 0x5A0AC80C

#define IPC_BOOTMODE_REG_CONTENT_100_CM 0x5A0A640C //If CM-Core runs on 100 MHz

#define IPC_BOOTMODE_REG_CONTENT_120_CM 0x5A0A780C //If CM-Core runs on 120 MHz

#pragma DATA_SECTION("MSGRAM_CPU1_TO_CPU2")

volatile UInt16 txMsgramToCPU2[IPC_MSGRAM_SIZE];

#pragma DATA_SECTION("MSGRAM_CPU2_TO_CPU1")

volatile UInt16 rxMsgramFromCPU2[IPC_MSGRAM_SIZE];

#pragma DATA_SECTION("MSGRAM_CPU_TO_CM")

volatile UInt16 txMsgramToCM[IPC_MSGRAM_SIZE];

#pragma DATA_SECTION("MSGRAM_CM_TO_CPU")

volatile UInt16 rxMsgramFromCM[IPC_MSGRAM_SIZE];

if(core == CPU_CPU2)

{

bootAddress = MSGRAM_BOOT_SECTOR_CPU2;

bootModeRegContent = IPC_BOOTMODE_REG_CONTENT_CPU2;

targetCpu = TO_CPU2;

txMsgram = txMsgramToCPU2;

archAddrInc = 1;

}

else if(core == CPU_CM)

{

bootAddress = MSGRAM_BOOT_SECTOR_CM;

bootModeRegContent = IPC_BOOTMODE_REG_CONTENT_120_CM;

targetCpu = TO_CM;

txMsgram = txMsgramToCM;

archAddrInc = 2;

}

After copying the bootup code to the desired message rams, my boot configuration of the CO-CPUs is this:

pModule->IPC_Boot_Pump_Reg->IPC_BOOTMODE = bootModeRegContent;

pModule->IPC_Flag_Ctr_Reg->IPC_SET = IPC_FLAG0;

if(core == CPU_CPU2)

{

SysCtl_controlCPU2Reset(SYSCTL_CORE_DEACTIVE);

while(SysCtl_isCPU2Reset() == true);

}

else

{

SysCtl_controlCMReset(SYSCTL_CORE_DEACTIVE);

while(SysCtl_isCMReset() == true);

}

timeStamp = time::getSystemTime100us();

while(pModule->IPC_Flag_Ctr_Reg->IPC_STS & IPC_FLAG0)

{

//wait till the CORE has acknowledge the configuration

if((time::getSystemTime100us() - timeStamp) > 5000)

{

//DEBUG

debug::time[targetCpu] = time::getSystemTime100us() - timeStamp;

debug::targetCpu = targetCpu;

debug::IPC_BootPumpReg[targetCpu].IPC_BOOTMODE = pModule->IPC_Boot_Pump_Reg->IPC_BOOTMODE;

debug::IPC_BootPumpReg[targetCpu].IPC_BOOTSTS = pModule->IPC_Boot_Pump_Reg->IPC_BOOTSTS;

debug::IPC_BootPumpReg[targetCpu].IPC_PUMPREQUEST = pModule->IPC_Boot_Pump_Reg->IPC_PUMPREQUEST;

debug::IPC_Flag_Ctr_Reg[targetCpu].IPC_ACK = pModule->IPC_Flag_Ctr_Reg->IPC_ACK;

debug::IPC_Flag_Ctr_Reg[targetCpu].IPC_CLR = pModule->IPC_Flag_Ctr_Reg->IPC_CLR;

debug::IPC_Flag_Ctr_Reg[targetCpu].IPC_COUNTERH = pModule->IPC_Flag_Ctr_Reg->IPC_COUNTERH;

debug::IPC_Flag_Ctr_Reg[targetCpu].IPC_COUNTERL = pModule->IPC_Flag_Ctr_Reg->IPC_COUNTERL;

debug::IPC_Flag_Ctr_Reg[targetCpu].IPC_FLG = pModule->IPC_Flag_Ctr_Reg->IPC_FLG;

debug::IPC_Flag_Ctr_Reg[targetCpu].IPC_RSVDREG = pModule->IPC_Flag_Ctr_Reg->IPC_RSVDREG;

debug::IPC_Flag_Ctr_Reg[targetCpu].IPC_SET = pModule->IPC_Flag_Ctr_Reg->IPC_SET;

debug::IPC_Flag_Ctr_Reg[targetCpu].IPC_STS = pModule->IPC_Flag_Ctr_Reg->IPC_STS;

//DEBUG

return PROCESS_TIMEOUT;

}

}

//DEBUG

debug::time[targetCpu] = time::getSystemTime100us() - timeStamp;

debug::targetCpu = targetCpu;

debug::IPC_BootPumpReg[targetCpu].IPC_BOOTMODE = pModule->IPC_Boot_Pump_Reg->IPC_BOOTMODE;

debug::IPC_BootPumpReg[targetCpu].IPC_BOOTSTS = pModule->IPC_Boot_Pump_Reg->IPC_BOOTSTS;

debug::IPC_BootPumpReg[targetCpu].IPC_PUMPREQUEST = pModule->IPC_Boot_Pump_Reg->IPC_PUMPREQUEST;

debug::IPC_Flag_Ctr_Reg[targetCpu].IPC_ACK = pModule->IPC_Flag_Ctr_Reg->IPC_ACK;

debug::IPC_Flag_Ctr_Reg[targetCpu].IPC_CLR = pModule->IPC_Flag_Ctr_Reg->IPC_CLR;

debug::IPC_Flag_Ctr_Reg[targetCpu].IPC_COUNTERH = pModule->IPC_Flag_Ctr_Reg->IPC_COUNTERH;

debug::IPC_Flag_Ctr_Reg[targetCpu].IPC_COUNTERL = pModule->IPC_Flag_Ctr_Reg->IPC_COUNTERL;

debug::IPC_Flag_Ctr_Reg[targetCpu].IPC_FLG = pModule->IPC_Flag_Ctr_Reg->IPC_FLG;

debug::IPC_Flag_Ctr_Reg[targetCpu].IPC_RSVDREG = pModule->IPC_Flag_Ctr_Reg->IPC_RSVDREG;

debug::IPC_Flag_Ctr_Reg[targetCpu].IPC_SET = pModule->IPC_Flag_Ctr_Reg->IPC_SET;

debug::IPC_Flag_Ctr_Reg[targetCpu].IPC_STS = pModule->IPC_Flag_Ctr_Reg->IPC_STS;

//DEBUG

return PROCESS_FINISHED;

CPU2 seems to start without problems. The code runs to the return PROCESS_FINISHED state My Debug variables has this content:

ipc::debug::time unsigned long[2] [68,5001] 0x0000B37C@Data

[0] unsigned long 68 0x0000B37C@Data

[0] struct IPC_Boot_Pump_Reg_t {IPC_BOOTSTS=0x00000000,IPC_BOOTMODE=0x5A0AC80C,IPC_PUMPREQUEST=0x00000000} (Hex) 0x0000B322@Data

IPC_BOOTSTS unsigned long 0x00000000 (Hex) 0x0000B322@Data

IPC_BOOTMODE unsigned long 0x5A0AC80C (Hex) 0x0000B324@Data

IPC_PUMPREQUEST unsigned long 0x00000000 (Hex) 0x0000B326@Data

[0] struct IPC_Flag_Ctr_Reg_t {IPC_ACK=0x00000000,IPC_STS=0x00000000,IPC_SET=0x00000000,IPC_CLR=0x00000000,IPC_FLG=... (Hex) 0x0000B2A2@Data

IPC_ACK unsigned long 0x00000000 (Hex) 0x0000B2A2@Data

IPC_STS unsigned long 0x00000000 (Hex) 0x0000B2A4@Data

IPC_SET unsigned long 0x00000000 (Hex) 0x0000B2A6@Data

IPC_CLR unsigned long 0x00000000 (Hex) 0x0000B2A8@Data

IPC_FLG unsigned long 0x00000001 (Hex) 0x0000B2AA@Data

IPC_RSVDREG unsigned long 0x00000000 (Hex) 0x0000B2AC@Data

IPC_COUNTERL unsigned long 0xE5D488E9 (Hex) 0x0000B2AE@Data

IPC_COUNTERH unsigned long 0x00000072 (Hex) 0x0000B2B0@Data

The CM Core stucks with IPCBOOTSTS content 0x80801004 (Bit 23 - Had fault occured).

The code runs to the `PROCESS_TIMEOUT` state -> This is the content of my Debug variables

ipc::debug::time unsigned long[2] [68,5001] 0x0000B37C@Data

[0] unsigned long 68 0x0000B37C@Data

[1] unsigned long 5001 0x0000B37E@Data

[1] struct IPC_Boot_Pump_Reg_t {IPC_BOOTSTS=0x80801004,IPC_BOOTMODE=0x5A0A780C,IPC_PUMPREQUEST=0x00000000} (Hex) 0x0000B328@Data

IPC_BOOTSTS unsigned long 0x80801004 (Hex) 0x0000B328@Data

IPC_BOOTMODE unsigned long 0x5A0A780C (Hex) 0x0000B32A@Data

IPC_PUMPREQUEST unsigned long 0x00000000 (Hex) 0x0000B32C@Data

[1] struct IPC_Flag_Ctr_Reg_t {IPC_ACK=0x00000000,IPC_STS=0x00000001,IPC_SET=0x00000000,IPC_CLR=0x00000000,IPC_FLG=... (Hex) 0x0000B2B2@Data

IPC_ACK unsigned long 0x00000000 (Hex) 0x0000B2B2@Data

IPC_STS unsigned long 0x00000001 (Hex) 0x0000B2B4@Data

IPC_SET unsigned long 0x00000000 (Hex) 0x0000B2B6@Data

IPC_CLR unsigned long 0x00000000 (Hex) 0x0000B2B8@Data

IPC_FLG unsigned long 0x00000001 (Hex) 0x0000B2BA@Data

IPC_RSVDREG unsigned long 0x00000000 (Hex) 0x0000B2BC@Data

IPC_COUNTERL unsigned long 0x33B8A446 (Hex) 0x0000B2BE@Data

IPC_COUNTERH unsigned long 0x00000071 (Hex) 0x0000B2C0@Data

In the first place I thought if everything is correct I have to see my code at the RAM locations M!-RAM for CPU2 and S0-RAM for CM. As you see from the screenshots I only read `0000`.

As you can see I perform the boot up procedere as described in Table 5-19 and 5-20 @ tech.- ref guide

I hope you can help me with this. Let me know if you need more information.

Best regards

Christian Peters