Hi.

I am developing using the 28388D.

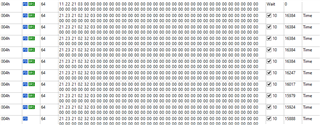

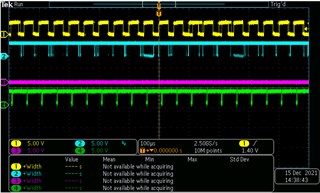

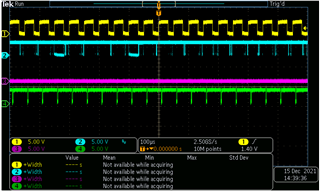

CAN-FD, a necessary function, is being implemented.

TX is polling, and RX is an interrupt.

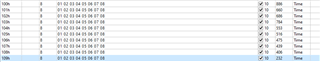

So, I searched for related examples in C2000 of V304 and V400 and tried to run them.

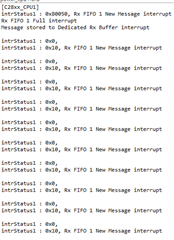

In the example of mcan_ex_2_external_loopback_receive of V304, it is confirmed that the interrupt is performed only once when data is received.

Is it true that the example provided really only has onetime receive interrupt?

Am I doing something wrong?

And, when an error interrupt occurs, is there any action other than clearing it?