Other Parts Discussed in Thread: TINA-TI

Hi team,

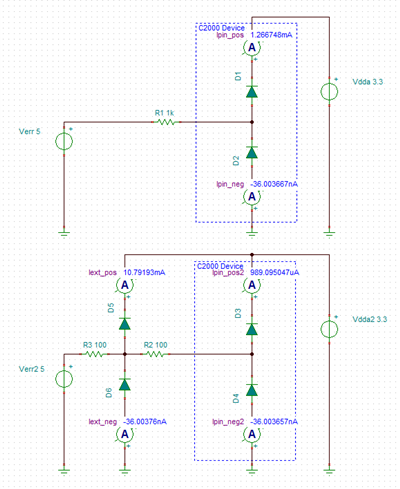

Is there any concern if opamp buffer to GPIO is powered by 5V (which is exceeding 3.6V rating) to buffer a 2.5V DC voltage to C2000? In the case of opamp failure, or 2.5V failure, there is a possibility of having >3.6V at GPIO pin.

How about to use an external series resistor (say >2.5kohm) to limit any potential current injected to the pin <2mA? Is this acceptable?