Part Number: TMS320F280023C

Other Parts Discussed in Thread: SYSCONFIG, LAUNCHXL-F280025C

Hi

I have setup the watchdog to trigger after 209 mS.

So far I have _NOT_ setup any servicing of the watchdog, so it should just re-reset my device in Infinity, or to i pull the plug.

And indeed after first powerup it resets the device, and continuous to do so for some time, but then it stops doing that.

First i thought the device was stuck in some NMI or exception of some sort. But it turns out it is running fine, and my application code is running as if no watchdog present.

So in short

Exspected:

Device reset every 209 mS until power is removed.

Reality:

Device reset every 209 mS for some time then the reset event stops, and the cpu runs normal SW.

"some time" = variable time frm 2 seconds to 20 seconds approximately.

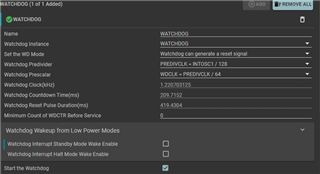

The watchdog is set using the Sysconfig tool:

With 209 mS run time it is plenty time to print out some debug information on my serial port.

So I added this just after serial init

Log_debug("WatchDog counter value = %u\r\n", SysCtl_getWatchdogCounterValue());

Log_debug("WatchDog reset status = %d\r\n", SysCtl_getWatchdogResetStatus());

Log_debug("Sys control and status register = %X\r\n", HWREGH(WD_BASE + SYSCTL_O_SCSR));

Log_debug("WatchDog KEY register = %X\r\n", HWREGH(WD_BASE + SYSCTL_O_WDKEY));

Log_debug("WatchDog status register = %X\r\n", HWREGH(WD_BASE + SYSCTL_O_WDCR));

Log_debug("WatchDog Windowed status register = %X\r\n", HWREGH(WD_BASE + SYSCTL_O_WDWCR));

* Log_debug is just macro expanding in to printf

From that I get

DBG: WatchDog counter value = 1 DBG: WatchDog reset status = 0 DBG: Sys control and status register = 5 DBG: WatchDog KEY register = 7 DBG: WatchDog status register = E07 DBG: WatchDog Windowed status register = 0

This show the same values both when a reset is later triggered and when not.

I also have these values printed on command in my testmonitor, and when I ask for them after the reset stopped happening I still get the same values except for the counter that keeps changing (indicating that it is running)

So why do my watchdog stop working?