Part Number: TMS320F28388D

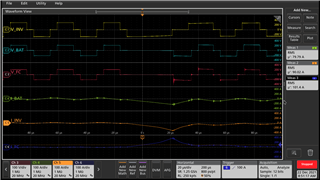

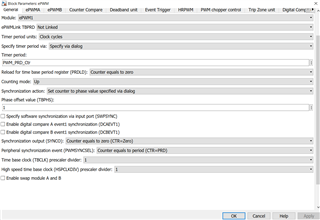

I am using EPWM1 to EPWM6 with switching frequency of 30 kHz and EPWM7 with switching frequency of 120 kHz. PWMs are synched with the master (ePWM1). Deadband is 1 us. CMPA and CMPB are constant and equal to half of the cycle. When some of the phase shifts get close to zero, we randomly miss a whole cycle on all the PWMs other than the main one. ePWM2, ePWM4 and ePWM 6 have phase shifts that are higher than half cycle and ePMW3 and ePWM4 have small phase shifts when the random skipping of cycles happens.