Part Number: TMS320F280049

Dear team:

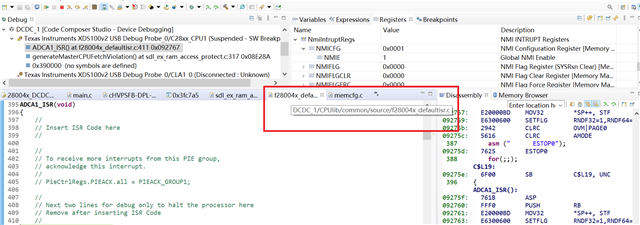

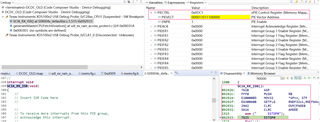

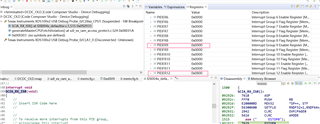

After my customer sets the CPU fetch protection for "ramg0", the program will enter the illegalisr (), but then the program will enter the SCIA again_ RX_ ISR()。 However, the interrupt is not enabled in his program, and the read pieier is also closed. Why jump into the interrupt?

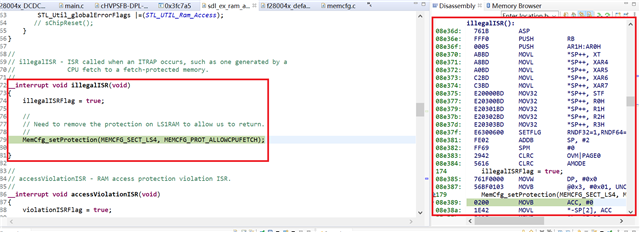

__interrupt void illegalISR(void)

{

illegalISRFlag = true;

MemCfg_setProtection(MEMCFG_SECT_GS0, MEMCFG_PROT_ALLOWCPUFETCH);

}

Best regards