Hello All,

I want to Reset CM core when received an explicit Command over TCP. How I achieve it ?

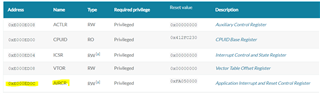

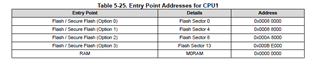

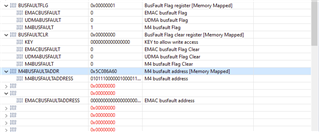

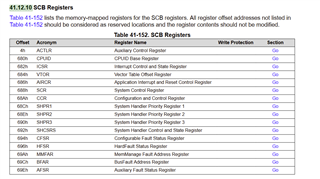

I have gone through TRM Chapter41 and found below table:

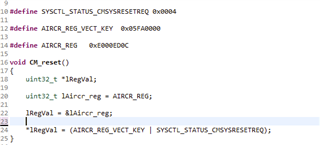

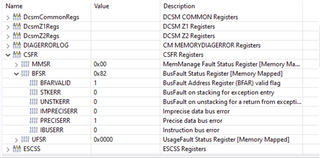

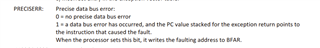

And I want to set SYSRESETREQ bit to 1 in AIRCR register.

But I'm unable to find its base address and thereby not able to access it.

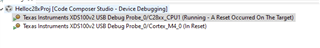

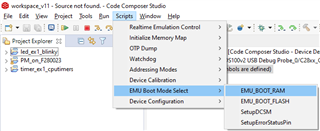

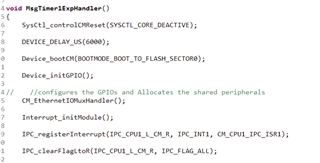

Is there any way I can Reset CM Core so that it will boot from Bootloader stage (If possible without resetting debugger).

Thanks and regards,

pranay