Other Parts Discussed in Thread: TMDSCNCD280049C, C2000WARE

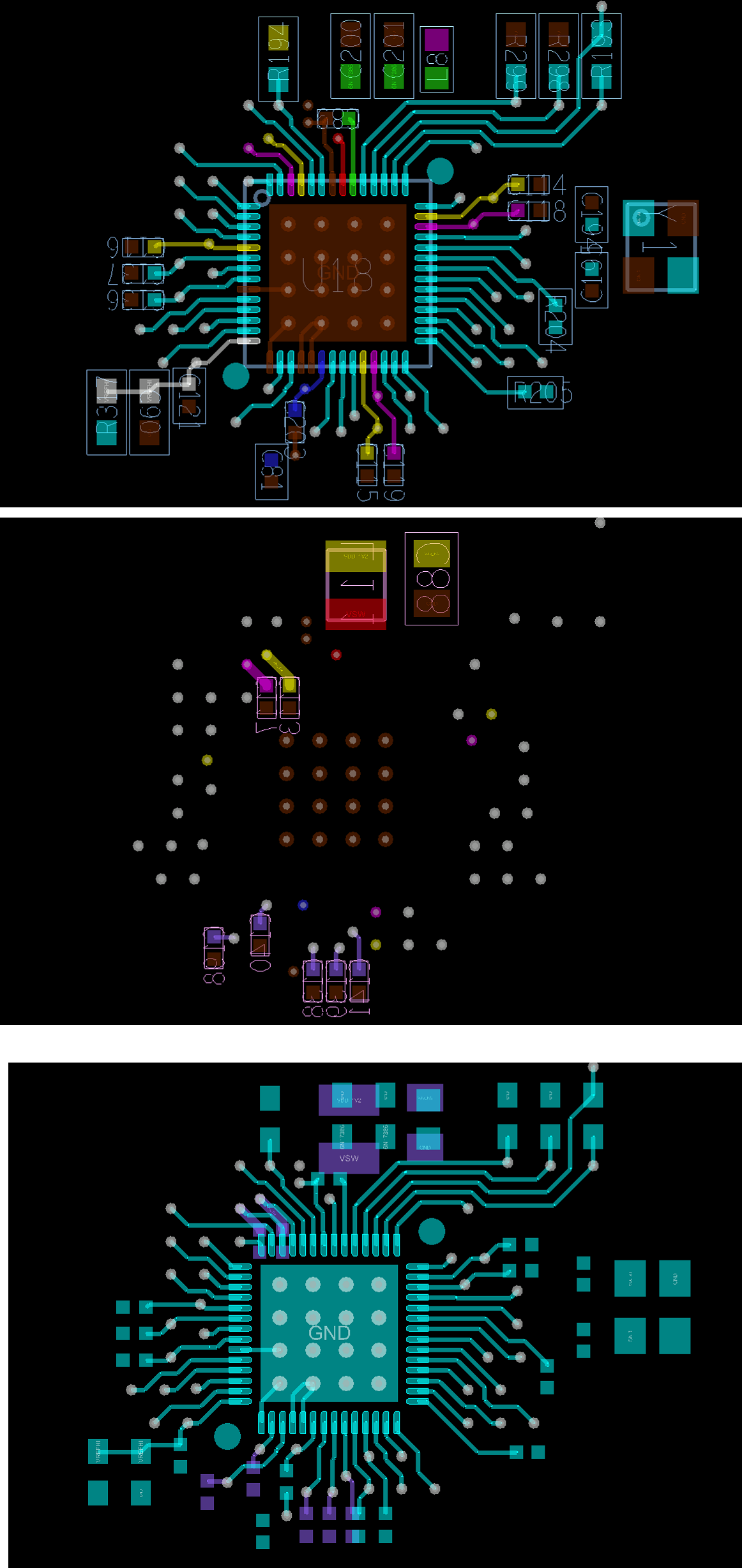

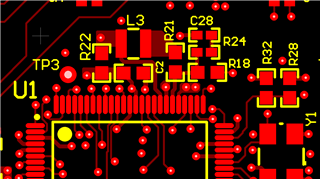

Hello, I'm currently working on a custom board using the RSH/VQFN56 package for the F28004x devices. Fanout is tricky when all the supply bypassing caps are on the top layer, along with the inductor for the integrated DCDC. I'm wondering which, if any, of these components, can be moved to the bottom side of the board, but can't find any reference designs using this package.

I also see section 7.9.1.2.1 in the datasheet, giving recommendations on the layout, but it's hard to make sense of some of these without some sort of picture (especially the one mentioning a "separate island or surgical cut in the ground plane").

Please advise,

Mike