- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello,

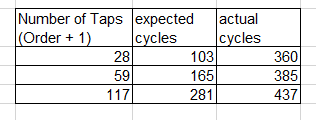

I am trying to use the FIR_f32_calc, in the FPU DSP Software Library User's Guide, as described on page 69 of the Oct 19, 2021 version. I'm using the version in C2000Ware_4_00_00_00, for a F2837xD processor. On page 69, they the number of taps, and expected cycles in Table 5.37. But I'm coming out well beyond those cycles, as the following expected versus actual tables shows.

Both my coefficient and state buffers are in internal ram, and aligned to 2 x (filter order + 1), as indicated in the User's Guide for that call. I just went ahead and used the DATA_ALIGN( variable, 256) pragma on both, to cover all 3 test cases.

Can you please provide any insight into something I may be overlooking, causing this mismatch between the expected cycles, and what I'm getting.

Regards,

Robert

This ended up being primarily due to the FIR_f32_calc running out of flash. After copying the associated assembly functions into RAM at startup, my 'cycles used' were as good, or better than those indicated in the User's Guide.

Thanks,

Robert