Hi,

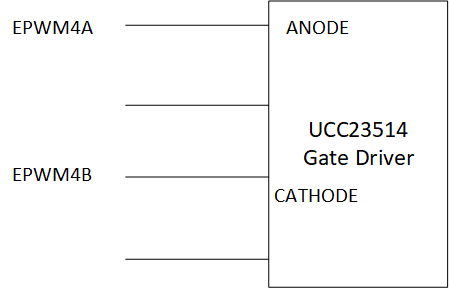

I am using 28379D T1/T2 event inside the EPWM action qualifier to regulate the sync buck inductor current. For testing, I am using a fixed 50% duty ratio. Part of ePWM is shown below. DCAEVT2 from CMPSS is linked to T2 event source.

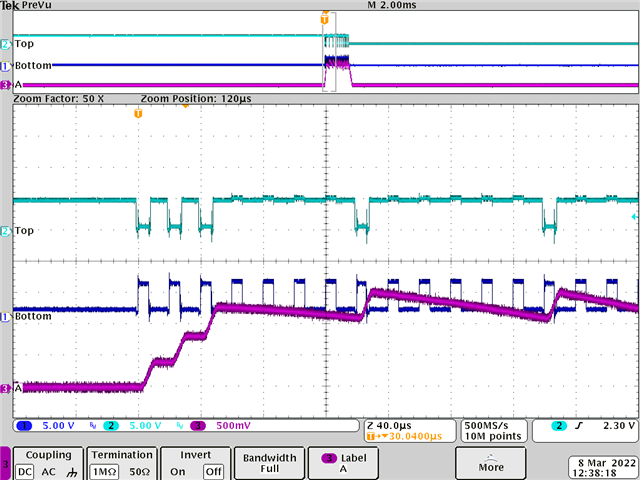

I record the test waveform. Light blue is the inductor voltage and Purple is the inductor current. I can see the current was able to regualted by the ePWM module, but there are some short pulses, which happened unexpected (close to the second cursor). Since I only make the EPWM output high when the counter equal to CMPA, the voltage pulse can only happen every 20 us, but that unexpected short pulse happens about 65us after the previous one. When ePWM counter is counting up, if T2 event becomes false (inductor current drops below threshold) after counter is greater than CMPA, will the EPWM still try to output high? It seems to me this is the only possibility to make this short pulse happen. Is there a way we can avoid this short pulse by keep using T1/T2 event?

I am looking foreard to your reply!

EPwm4Regs.CMPA.bit.CMPA = 250;

EPwm4Regs.TBPHS.all = 0;

EPwm4Regs.TBCTL.bit.PHSEN = TB_ENABLE; //slave mode

EPwm4Regs.TBCTL.bit.PRDLD = TB_SHADOW;

EPwm4Regs.TBCTL.bit.SYNCOSEL = TB_SYNC_IN; //sync flow-through

EPwm4Regs.TBPRD = 500; // 500*2*0.02= 20 us for up and down

EPwm4Regs.TBCTL.bit.CTRMODE = TB_COUNT_UPDOWN;

EPwm4Regs.AQCTLA.bit.CAU = AQ_SET;

EPwm4Regs.AQCTLA.bit.CAD = AQ_CLEAR;

EPwm4Regs.AQCTLA2.bit.T2U = AQ_CLEAR; // if over-current, upper switch output low

EPwm4Regs.AQCTLA2.bit.T2D = AQ_CLEAR; // if over-current, upper switch output low

EPwm4Regs.DBCTL.bit.OUT_MODE = DB_FULL_ENABLE; // Dead-band module

EPwm4Regs.DBCTL.bit.POLSEL = DB_ACTV_HIC; // Active High Compli

EPwm4Regs.DBFED.all = 50; // 1 us deadtime

EPwm4Regs.DBRED.all = 50; // 1 us deadtime

EPwm4Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;

EPwm4Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;

EPwm4Regs.CMPCTL.bit.LOADAMODE = CC_CTR_ZERO; //load on CTR = zero

EPwm4Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO; //load on CTR = zero

EPwm4Regs.DCTRIPSEL.bit.DCAHCOMPSEL = 3; // Take EPWM Trip 4 from Xbar

EPwm4Regs.TZDCSEL.bit.DCAEVT2 = 2; // DCAEVT2 happens when DCAH becomes high

EPwm4Regs.DCACTL.bit.EVT2FRCSYNCSEL = 1; // No sync needed

EPwm4Regs.AQTSRCSEL.bit.T2SEL= 1; // Select DCAEVT2 as T2 event source