Part Number: TMS320F280025

Other Parts Discussed in Thread: SYSCONFIG, C2000WARE

I opened a thread some time ago but could not resolve the issue at that time. We have configured some PWMs for 20 KHz frequency and centre aligned mode. The setup code is given below:

// Set-up TBCLK

//Device clock is 100 MHz

EPWM_setTimeBasePeriod(base, 2500);

EPWM_setPhaseShift(base, 0U);

EPWM_setTimeBaseCounter(base, 0U);

EPWM_setTimeBaseCounterMode(base, EPWM_COUNTER_MODE_UP_DOWN);

EPWM_disablePhaseShiftLoad(base);

//

// Set ePWM clock pre-scaler

//

EPWM_setClockPrescaler(base, EPWM_CLOCK_DIVIDER_1, EPWM_HSCLOCK_DIVIDER_1);

//

// Set up shadowing

//

EPWM_setCounterCompareShadowLoadMode(base, EPWM_COUNTER_COMPARE_A,

EPWM_COMP_LOAD_ON_CNTR_ZERO);

//

// Set actions

//

EPWM_setActionQualifierAction(base, EPWM_AQ_OUTPUT_A, EPWM_AQ_OUTPUT_LOW,

EPWM_AQ_OUTPUT_ON_TIMEBASE_ZERO);

EPWM_setActionQualifierAction(base, EPWM_AQ_OUTPUT_A, EPWM_AQ_OUTPUT_HIGH,

EPWM_AQ_OUTPUT_ON_TIMEBASE_UP_CMPA);

EPWM_setActionQualifierAction(base, EPWM_AQ_OUTPUT_A,

EPWM_AQ_OUTPUT_NO_CHANGE,

EPWM_AQ_OUTPUT_ON_TIMEBASE_PERIOD);

EPWM_setActionQualifierAction(base, EPWM_AQ_OUTPUT_A, EPWM_AQ_OUTPUT_LOW,

EPWM_AQ_OUTPUT_ON_TIMEBASE_DOWN_CMPA);

EPWM_setActionQualifierAction(base, EPWM_AQ_OUTPUT_B,

EPWM_AQ_OUTPUT_LOW,

EPWM_AQ_OUTPUT_ON_TIMEBASE_ZERO);

EPWM_setActionQualifierAction(base, EPWM_AQ_OUTPUT_B,

EPWM_AQ_OUTPUT_HIGH,

EPWM_AQ_OUTPUT_ON_TIMEBASE_UP_CMPB);

EPWM_setActionQualifierAction(base, EPWM_AQ_OUTPUT_B,

EPWM_AQ_OUTPUT_NO_CHANGE,

EPWM_AQ_OUTPUT_ON_TIMEBASE_PERIOD);

EPWM_setActionQualifierAction(base, EPWM_AQ_OUTPUT_B,

EPWM_AQ_OUTPUT_LOW,

EPWM_AQ_OUTPUT_ON_TIMEBASE_DOWN_CMPB);

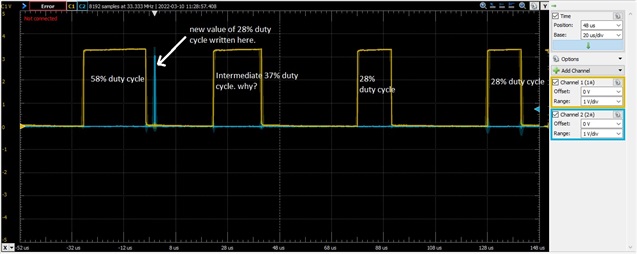

We had observed that there is an intermediate transition in duty cycle of the PWM whenever its duty cycle is changes. Please refer to the image below:

Initially the duty cycle is setup for 50%. Then at some instant shown by blue line the duty cycle us written for 28% We are using following function:

EPWM_setCounterCompareValue(base, EPWM_COUNTER_COMPARE_A,

duty_cycle_count);

However you can see that there is an intermediate period having duty cycle of 37%. We did the setting according to our understanding that the new counter value will take effect from the start of the next PWM period.

EPWM_setCounterCompareShadowLoadMode(base, EPWM_COUNTER_COMPARE_A,

EPWM_COMP_LOAD_ON_CNTR_ZERO);

However we suspect that this is happening since the new counter value is taking effect in the middle of the period. How can we ensure that the duty cycle takes effect from the start of the period so that there is direct transition to our next intended duty cycle.