Part Number: TMS320F28379S

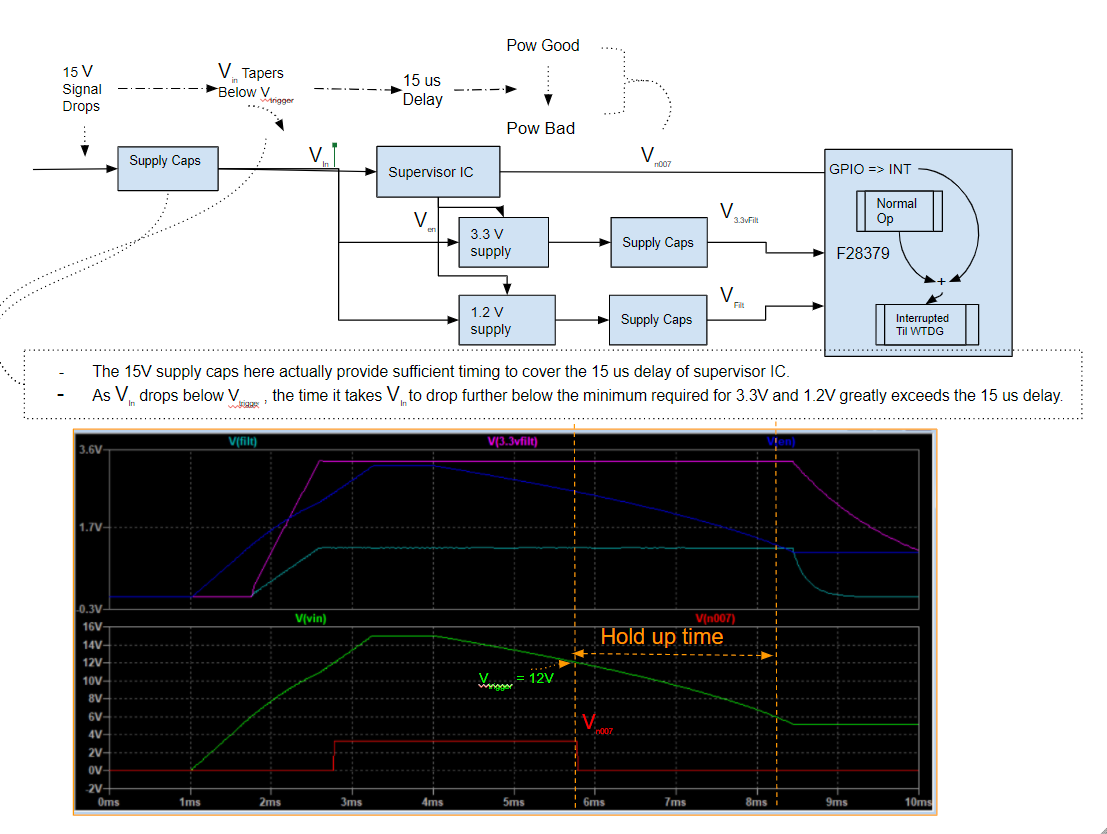

asking for any input regarding any established procedure in the event of an unexpected power failure where some supply capacitance would provide a runtime window before power down of mcu. Specifically for the purpose of executing writes to flash. Also, what would be expected cycle counts per flash word write? What would variance be with and without ecc?

High level is envisioned as

1. GPIO detection of power loss triggers an unmaskable interrupt

2. pre specified volatile memory is written to pre erased nv memory.

I understand this is somewhat generic so any helpful resources is appreciated.

Regards,

Tyler