I'm getting an unexpected SCI interrupt that causes the code to stop running. Here's the setup:

C2000 (TMS320F28379D) > SCI peripheral > externally connected to an RS-422 transceiver chip > switch

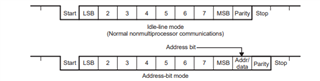

The purpose of the switch is to loopback the outputs of the transceiver chip to the inputs of the transceiver chip so we can easily run a serial loopback test with some dummy data using the C2000 SCI peripheral. Unfortunately, when we specifically switch from the loopback position to the open position (output/transmit is not looped back to input/receive) we observed via an oscilloscope that there are some voltage level changes, and if we switch it slow enough we see the serial input (rx) line go from high to low and then it stays low.

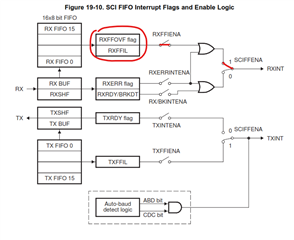

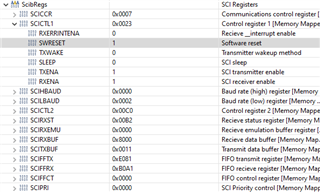

When the serial input line stays low we also observed the code gets "stuck" and when I connect a debugger and pause the execution it is in the SCI rx interrupt. Why would the SCI receive line being held low or transitioning from high to low cause the code to stop executing? Is it being faked out and it can't recover from this condition?

Thanks!