Other Parts Discussed in Thread: TMS320F28027

Hi All,

I recently started a project using a LaunchPadXL TMS320F2802x. I started with an example and added some simple test code to exercise the SCIA and I2C interfaces, one project file at a time.

Now, I have target prototype hardware in-hand that contains a TMS320F28020 MCU. The memory map of the 28020 is smaller than the LaunchPad's 28027. So, now when I compile the same code to run in the smaller memory space, I get an error indicating reference to a memory region that doesn't exist, like this:

C28xx: Loader: One or more sections of your program falls into a memory region that is not writable. These regions will not actually be written to the target. Check your linker configuration and/or memory map.

I'm having a hard time understanding the different linker command files and other references to memory mapping.

The memory map file generated during the make process shows RAML0 starting at 0x8000 and extending into 0x85ff as follows:

MEMORY CONFIGURATION

name origin length used unused attr fill

---------------------- -------- --------- -------- -------- ---- --------

PAGE 0:

BEGIN 00000000 00000002 00000002 00000000 RWIX

RAMM0 00000050 000003b0 000003b0 00000000 RWIX

RAML0 00008000 00000600 00000377 00000289 RWIX

FLASHC 003f2000 00002000 00000000 00002000 RWIX

IQTABLES 003fe000 00000b50 00000000 00000b50 RWIX

IQTABLES2 003feb50 0000008c 00000000 0000008c RWIX

IQTABLES3 003febdc 000000aa 00000000 000000aa RWIX

BOOTROM 003ff27c 00000d44 00000000 00000d44 RWIX

RESET 003fffc0 00000002 00000000 00000002 RWIX

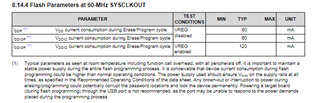

However, the 28020 physical RAML0 memory starts at 0x8000 and only extends to 0x83ff.

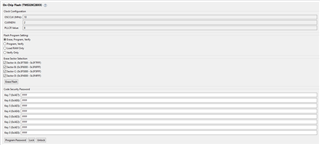

At first, I thought this was because the setting in the project >Properties>CCS General Project tab was set to Variant TMS320F28027:

But, when I changed it to 28020, I got multiple duplicate memory range errors:

I will need to manipulate the memory map before the project is done in several ways to fit all the code into available memory. I could use some help understanding the appropriate ways to modify the memory map.

I have used the linker command file to make minor changes in the past, so I understand that part of it, but I don't know why the linker still thinks RAML0 is the longer than it really is.

Questions:

1. Why does the make file end up with a memory map that includes address space that doesn't exist in the physical part?

2. Where is it getting the linker command file that tells it each memory's location and size? The linker command file that was copied into the project folder after changing the Variant setting shows the correct length of RAML0.

3. How do .gel files factor into the equation?

4. Is there an app note describing the memory mapping configuration architecture? I'm looking for info about manipulating linker cmd files, gel files, properties settings, etc..

Thanks,

robin