Hello,

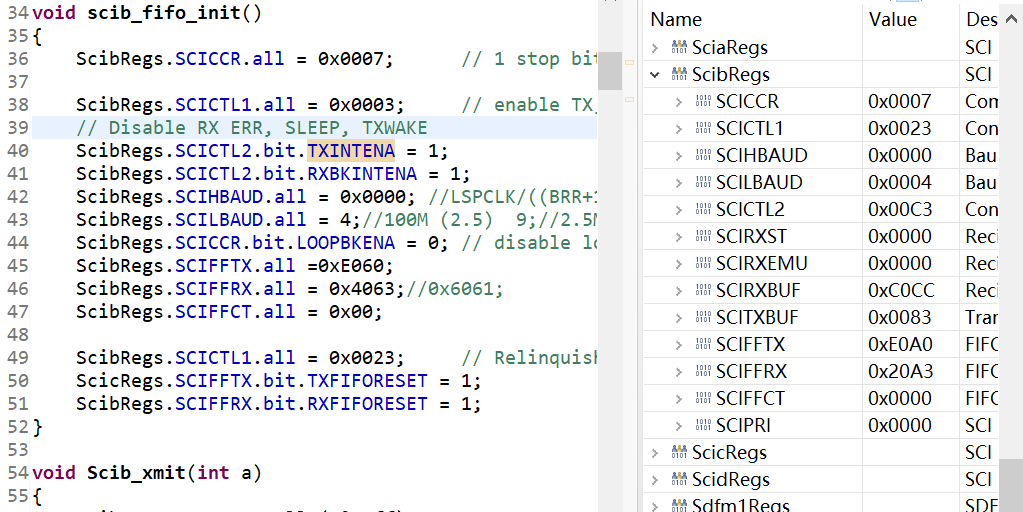

My question is: when using TMS320F28377SPZP to test SCI communication, the baud rate used is 2.5m (I have tried in the case of 1m to 5m, and there is the same problem). The upper computer sends 3 bytes of data, the header is 0x55, and the last two are data greater than 0x80. It often shows that the received data header is correct, The last two errors (0x55 is received correctly, the last two numbers are wrong, and the number less than 0x80 will appear. Most of the last two numbers are received as 0x00. For example, the upper computer sends 0x55,0x9f and 0xff, then sends 0x55,0xaf and 0xaf after an interval of 32us, and then sends 0x55,0xbf and 0xbf at an interval of 32us). These three strings of data are sent in a circular manner. After a period of time, the receiving end of 28377 will appear that the received data is 0x55,0x00,0x00, These three numbers (other numbers will appear in the last two, such as 0x46,0x01, mostly 0x00), and the value of scirxbuf is 0xc0cc.