Two pairs of complementary PWMs, i.e. EPWM1A/B and EPWM2A/B are used in my power converter application. The variable "CmdRun" is used to control all the 4 PWMs to run when set to 1 and stop when set to 0, respectively.

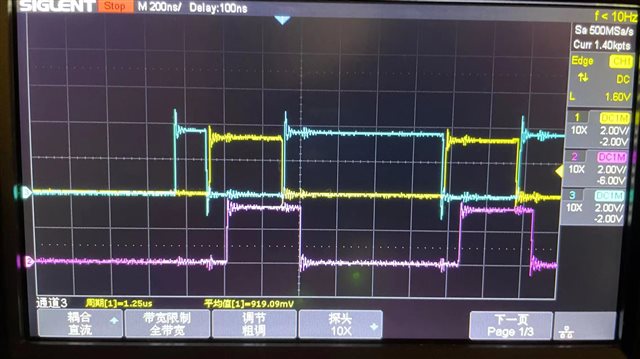

Requirement 1: The start-up sequence of 4 PWMs needs to be the same every time when CmdRun=1, as in initialized configuration (EPWM1 up-count mode, EPWM1.TPRD=100, EPWM1.CMPA=10, EPWM1.TBCTR = 0, AQ set on zero while clear on CPMA event; EPWM2 up-count mode, EPWM2.TPRD=100, EPWM2.CMPA=20, EPWM2.CMPB=50, EPWM2.TBCTR = 0, AQ set on CMPA while clear on CMPB event, TBCLK=EPWMCLK=100MHz).

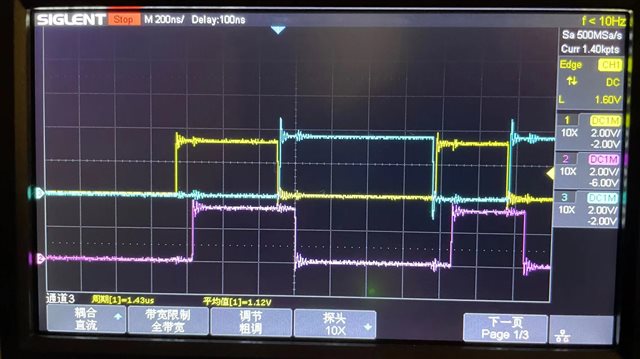

Requirment 2: For the stop sequence, when CmdRun=0, all the 4 PWMs shall be clear to low simultaneously, without even 10ns delay.

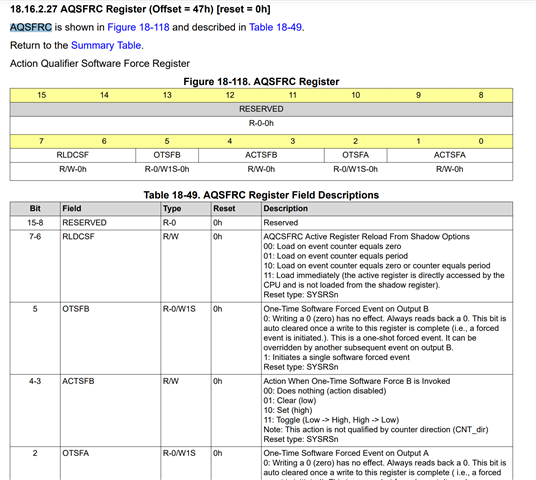

My current design is using the one-shot-trip (OST) via software. Some codes are provided as below. But it seems that the sequential execution of codes introduces some action delays. The EPWM2 will goes to run a little bit earlier than EPWM1 as it clears the OST condition before EPWM1. The EPWM1 will stop earlier than EPWM2 as it forces the OST before EPWM2. Can you give me some suggestions on how to realize the above mentioned requirements?

if (StateRun==0)

{

if (CmdRun==1)

{

EPwm1Regs.TBCTL.bit.SWFSYNC = 1; // Force the TBCTR to reset.

EALLOW;

EPwm2Regs.TZCLR.bit.OST = 1; // Clear the one-shot trip (OST) condition.

EPwm1Regs.TZCLR.bit.OST = 1; // Clear the one-shot trip (OST) condition.

CpuSysRegs.PCLKCR0.bit.TBCLKSYNC = 1; // All ePWM time-base clocks are started with the rising edge of TBCLK aligned.

EDIS;

StateRun = 1;

}

}

else

{

if (CmdRun==0)

{

EALLOW;

EPwm1Regs.TZFRC.bit.OST = 1; // Force a one-shot trip (OST) via software. Q1 first OFF.

EPwm2Regs.TZFRC.bit.OST = 1; // Force a one-shot trip (OST) via software.

CpuSysRegs.PCLKCR0.bit.TBCLKSYNC = 0; // The time-base clock of all ePWM modules is stopped.

EDIS;

EPwm1Regs.TBCTL.bit.SWFSYNC = 1; // Force the TBCTR to reset.

StateRun = 0;

}

}