Other Parts Discussed in Thread: DRV8301, , LAUNCHXL-F28027F, CONTROLSUITE, TMS320F28379D, MOTORWARE

Hello, I am working on BLDC sensored motor with lunchpadTMS320F29379D + DRV8305. my question is:

1. nfault pin always ON ,it is ok ?

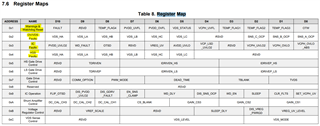

2. for SPI interface what configuration is required? I removed J1P,JP2 and JP3 . but not able to get output.

I take reference code for DRV8305 from INSTAPIN BLDC =>DRV8301.h library .