Other Parts Discussed in Thread: TMS320F28377D, UNIFLASH, C2000WARE

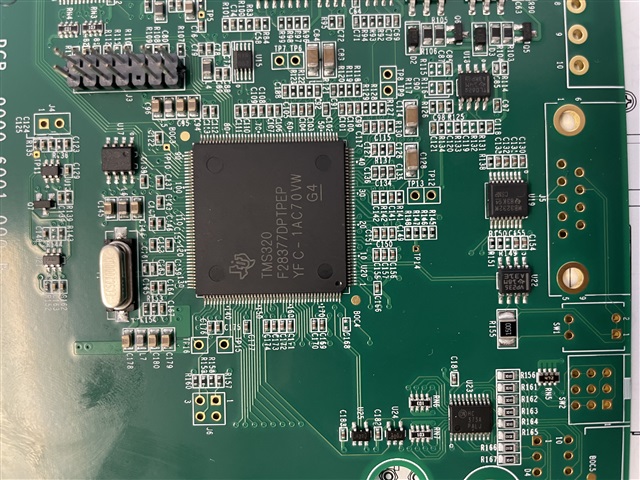

Due to the shortages of the 'TMS320F28377D' processor for our production runs we recently changed to using the TMS320F28377D-EP variant which was available despite its price difference. We made this decision based on this forum post: https://e2e.ti.com/support/microcontrollers/c2000-microcontrollers-group/c2000/f/c2000-microcontrollers-forum/1053170/tms320f28377d-ep-commercial-and-ep-difference

In our first production batch we have had 10 of our 200 board batch fail quality control during flash programming issues. We have produced over 700 of the same production boards previously using the TMS320F28377D processor without a single instance of flash programming difficulties. We have attempted to program these 10 failing boards using the following methods: Serial Flash, Uniflash, and CCS. We have tried both serial and the XDS2XX USB Debug Probe.

We've run out of ideas to for potential causes for these failures. We have checked the first couple returns from QC for bad traces, and any other physical level problems and found none.

I have trace logs from both Serial Flash programming and Uniflash if those will help. However the serial ones are quite large so if those are wanted I will send separately.

Here is the log from UniFlash:

volume_upVerboseClearClose

[6/3/2022, 10:52:01 AM] [INFO] C28xx_CPU1: GEL Output: Memory Map Initialization Complete

[6/3/2022, 10:52:01 AM] [INFO] C28xx_CPU2: GEL Output: Memory Map Initialization Complete

[6/3/2022, 10:52:02 AM] [INFO] C28xx_CPU1: Performing Security Operation...

[6/3/2022, 10:52:02 AM] [INFO] C28xx_CPU1: Calculated Link Pointer Offset: 0x20

[6/3/2022, 10:52:02 AM] [INFO] C28xx_CPU1: Unlocking device...

[6/3/2022, 10:52:02 AM] [INFO] C28xx_CPU1: Lock status: 0

[6/3/2022, 10:52:02 AM] [SUCCESS] C28xx_CPU1: Operation completed successfully.

[6/3/2022, 10:52:07 AM] [INFO] C28xx_CPU1: GEL Output: Memory Map Initialization Complete

[6/3/2022, 10:52:07 AM] [INFO] C28xx_CPU2: GEL Output: Memory Map Initialization Complete

[6/3/2022, 10:52:08 AM] [INFO] C28xx_CPU1: Writing Flash @ Address 0x00080000 of Length 0x00000002 (page 0)

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Error: (Error -1044 @ 0x0) The debug probe reported an error. Confirm debug probe configuration and connections, reset the debug probe, and retry the operation. (Emulation package 9.6.0.00172)

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Trouble Halting Target CPU: (Error -1135 @ 0xC095) The debug probe reported an error. Confirm debug probe configuration and connections, reset the debug probe, and retry the operation. (Emulation package 9.6.0.00172)

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Unable to determine target status after 20 attempts

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Failed to remove the debug state from the target before disconnecting. There may still be breakpoint op-codes embedded in program memory. It is recommended that you reset the emulator before you connect and reload your program before you continue debugging

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Error occurred during flash operation: Could not read 0x0007026D@Data: target is not connected

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Error occurred during flash operation: Could not write 0x0005F444@Data: target is not connected

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Error occurred during flash operation: Could not read 0x0005F444@Data: target is not connected

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Error occurred during flash operation: Could not read 0x000130@Program: target is not connected

[6/3/2022, 10:52:09 AM] [INFO] C28xx_CPU1: PLL configuration status = 0.

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Error executing PLL configuration algorithm. Operation cancelled. (0x0)

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Error occurred during flash operation: Could not write 0x0005D200@Data: target is not connected

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: File Loader: Memory write failed: Unknown error

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Error occurred during flash operation: Could not read register PC: target is not connected

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Error occurred during flash operation: Could not write 0x0005F800@Data: target is not connected

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Error occurred during flash operation: Could not write 0x000000@Program: target is not connected

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Error occurred during flash operation: Cannot enable while the target is disconnected

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Error occurred during flash operation: Could not read 0x0005F444@Data: target is not connected

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Error occurred during flash operation: Could not read 0x0007026D@Data: target is not connected

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Error occurred during flash operation: Could not write 0x0005F444@Data: target is not connected

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Error occurred during flash operation: Could not read 0x0005F444@Data: target is not connected

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Error occurred during flash operation: Failed to run target while trying to execute pwrite_en.alg

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Flash operation timed out waiting for the algorithm to complete. Operation cancelled.

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Perform a debugger reset and execute the Boot-ROM code (click on the RESUME button in CCS debug window) before erasing/loading the Flash. If that does not help to perform a successful Flash erase/load, check the Reset cause (RESC) register, NMI shadow flag (NMISHDFLG) register and the Boot-ROM status register for further debug.

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Error occurred during flash operation: Could not read 0x0007026D@Data: target is not connected

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Error occurred during flash operation: Could not write 0x0005F444@Data: target is not connected

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Error occurred during flash operation: Could not read 0x0005F444@Data: target is not connected

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Error occurred during flash operation: Could not read 0x0007026D@Data: target is not connected

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Error occurred during flash operation: Could not write 0x0005D200@Data: target is not connected

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Error occurred during flash operation: Could not read 0x05D200@Program: target is not connected

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Error occurred during flash operation: Could not read 0x0007026D@Data: target is not connected

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Error occurred during flash operation: Could not read 0x0005D20E@Data: target is not connected

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Error occurred during flash operation: Could not write 0x0005D20E@Data: target is not connected

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Error occurred during flash operation: Could not read 0x0005D20E@Data: target is not connected

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Error occurred during flash operation: Could not write 0x0005D20E@Data: target is not connected

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Error occurred during flash operation: Could not read 0x0005D22E@Data: target is not connected

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Error occurred during flash operation: Could not read 0x0005D208@Data: target is not connected

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Error occurred during flash operation: Could not write 0x0005D208@Data: target is not connected

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Error occurred during flash operation: Could not read 0x0005D208@Data: target is not connected

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Error occurred during flash operation: Could not write 0x0005D208@Data: target is not connected

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Error occurred during flash operation: Could not read 0x0005D222@Data: target is not connected

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Error occurred during flash operation: Could not write 0x0005D222@Data: target is not connected

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Error occurred during flash operation: Could not write 0x0005D214@Data: target is not connected

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Error occurred during flash operation: Could not read 0x0005D20E@Data: target is not connected

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Error occurred during flash operation: Could not write 0x0005D20E@Data: target is not connected

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Error occurred during flash operation: Could not write 0x0005D20E@Data: target is not connected

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Error occurred during flash operation: Could not write 0x0005D222@Data: target is not connected

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Error occurred during flash operation: Could not write 0x0005D200@Data: target is not connected

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Error occurred during flash operation: Could not write 0x000000@Program: target is not connected

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Error occurred during flash operation: Cannot enable while the target is disconnected

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Error occurred during flash operation: Could not read 0x0005F444@Data: target is not connected

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Error occurred during flash operation: Could not read 0x0007026D@Data: target is not connected

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Error occurred during flash operation: Could not write 0x0005F444@Data: target is not connected

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Error occurred during flash operation: Could not read 0x0005F444@Data: target is not connected

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Error occurred during flash operation: Failed to run target while trying to execute pwrite_dis.alg

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Flash operation timed out waiting for the algorithm to complete. Operation cancelled.

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Perform a debugger reset and execute the Boot-ROM code (click on the RESUME button in CCS debug window) before erasing/loading the Flash. If that does not help to perform a successful Flash erase/load, check the Reset cause (RESC) register, NMI shadow flag (NMISHDFLG) register and the Boot-ROM status register for further debug.

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Error occurred during flash operation: Could not read 0x0007026D@Data: target is not connected

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Error occurred during flash operation: Could not write 0x0005F444@Data: target is not connected

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Error occurred during flash operation: Could not read 0x0005F444@Data: target is not connected

[6/3/2022, 10:52:09 AM] [ERROR] C28xx_CPU1: Error occurred during flash operation: Could not write register PC: target is not connected

-Ben