Part Number: TMS320F28376S

Other Parts Discussed in Thread: C2000WARE

Hello everybody,

I have a problem, with sending the firmware with SCI using the example version called (F2837xS_sci_flash_kernel),

I put the recommendations seen in other posts here, including in the CMD file, like the ALIGN(8) example for the sectors.

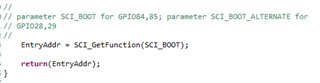

Another configuration made was so that the pins used correspond to my UART hardware, that is, the GPIO84 and GPIO85 pins are enabled.

The first used example version was (C2000Ware_4_01_00_00), that is, the current version.

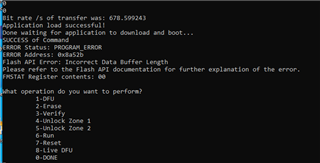

The kernel sent to the TMS went correctly and the menu was presented.

When sending the command (1-DFU) the sending of the application itself starts, this process takes time and always ends without success.

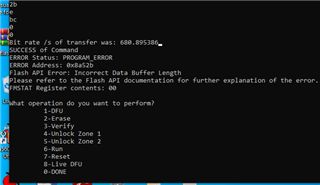

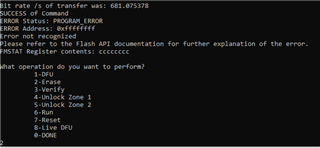

I tested the kernel version (C2000Ware_2_01_00_00) for comparison and got a different error.

Now I have 2 questions:

1- How to fix this problem?

2- How to increase the application sending speed?

command sent:

serial_flash_programmer.exe -d f2837xS -k C:\Users\rodrigo.stefanini\Desktop\FIRMWARE_F28376S\F2837xS_sci_flash_kernel.txt -a C:\Users\rodrigo.stefanini\Desktop\FIRMWARE_F28376S\F28376S_application.txt -p COM79 -b 38400