Other Parts Discussed in Thread: C2000WARE

The header file (DSP28_SWPrioritizedIsrLevels.h) required to control ePIE peripheral core priority levels (TRM 3.5.6 Vector Tables) is missing C2000ware V3.04/4.01 DSP folder. The ePIE MASK priory order document web page specifically states header file (DSP28_SWPrioritizedIsrLevels.h) is required.

Using the MASK Values

Within an interrupt service routine, the global and group priority can be changed by software to allow other interrupts to be serviced. The steps are the same as described before. The only difference is the mask values for IER and PIEIERx have been managed in the DSP28_SWPrioritizedIsrLevels.h file.

Why was the header file (DSP28_SWPrioritizedIsrLevels.h) remove from C2000ware?

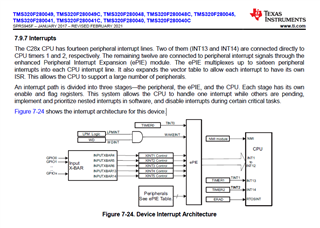

The peripherals all send ePIE a core priory value in order that higher priority groups are not stomped on by lower slower priority interrupts. Likewise, it should stop a lower priority peripheral from over running a higher priority group CPU instruction decode.

Currently without the header file SCIB INT9.4 overruns ADCA1 INT1.1 (higher core priority) before reaching SW Clear ACK placed at the bottom of INT1.1 ISR.

Why is the peripheral core priority values being ignored by ePIE and the CPU?