Other Parts Discussed in Thread: TMS320F28055, TMS320F28035

Hello folks,

I have 2 controllers connected via spi, one is the master and the other is the slave.

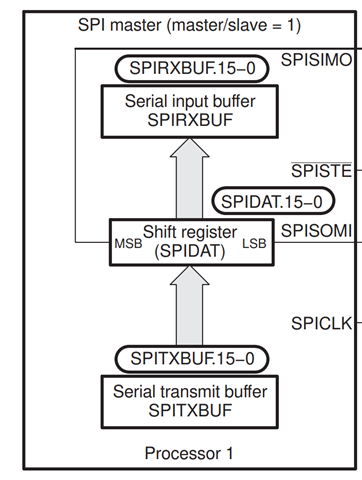

When I send data to the slave, the data arrives in the SPIDAT shift register.

The data should then be forwarded to the SPIRXBUF buffer.

I also have to say that I send 2x 8 bits.

When I try to send data, it always arrives in the SPIDAT shift register, which can be seen in debug mode, but the data is not always in the SPIRXBUF, sometimes it pushes it in and sometimes not completely.

About 4 times it works and then 1 time it doesn't work again. Can someone tell me where the problem is.

thank you for your help.

Kind regards

Markus