Part Number: LAUNCHXL-F280049C

Other Parts Discussed in Thread: SYSCONFIG

Hello,

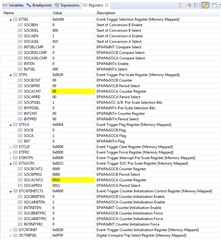

The ADC SOC is triggered by source EPWM via CMPD count matching has no time constraint over ISR decimation times. The code to configure CMPD as to match TBPRD counts for ADC EOC triggers has no effect on ISR idle execution time 5µs grow to 25µs. The minimum configured SOCA trigger time is set for 250µs match counts. Oddly TRM 18.4 Fig.18-4 CTR=PRD does not show an internal view how SOCA can be a trigger source for ADC EOC of any SOC#.

Please reference below code that SOCA is not triggering EOC for SOC's in any interval match counts configured for CMPD. Even CMPD 2500 match counts SOCA still triggers ADC EOC for 5µs idle, 25µs fully active. That ISR minimum 250µs time should be constrained by CMPD triggering the ADC SOC. The GPIO decimation pulse width (150µs) but that includes dead time outside the ISR loop, GPIO pulses are active high periods.

/* Clear the the EPWM trigger interrupts */

EPWM_disableInterrupt(obj->pwmHandle[0]);

// set the CMPD shadow load for period

EPWM_setCounterCompareShadowLoadMode(obj->pwmHandle[cnt],

EPWM_COUNTER_COMPARE_D,

EPWM_COMP_LOAD_ON_CNTR_PERIOD); //EPWM_COMP_LOAD_ON_CNTR_ZERO

// set EPWM1 trigger pulse, TBCTR=50µs*5 250µs or 25µs*1 CMPD-D

// setup the Event Trigger Selection Register (ETSEL)

EPWM_setADCTriggerSource(obj->pwmHandle[0], EPWM_SOC_A, EPWM_SOC_TBCTR_D_CMPD);

// Enable EPWM1 to trigger ADC0 sample event

EPWM_enableADCTrigger(obj->pwmHandle[0], EPWM_SOC_A);

// Clear INT flags and Event Trigger Clear Register (ETCLR)

EPWM_clearEventTriggerInterruptFlag(obj->pwmHandle[0]);

EPWM_clearADCTriggerFlag(obj->pwmHandle[0], EPWM_SOC_A);

// write value for ADC trigger (20KHz SOC_Int*5TBCTR=250µs, 1period=50µs)

EPWM_setCounterCompareValue(obj->pwmHandle[0], EPWM_COUNTER_COMPARE_D, 5);