Other Parts Discussed in Thread: C2000WARE

Hi all,

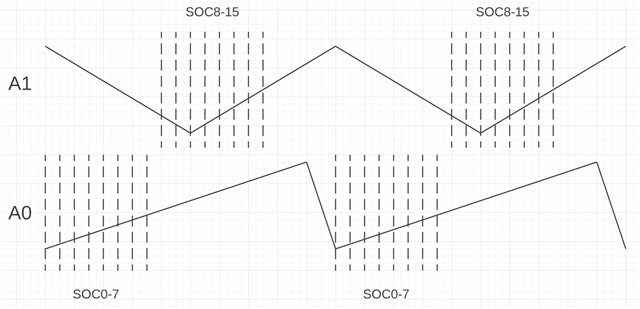

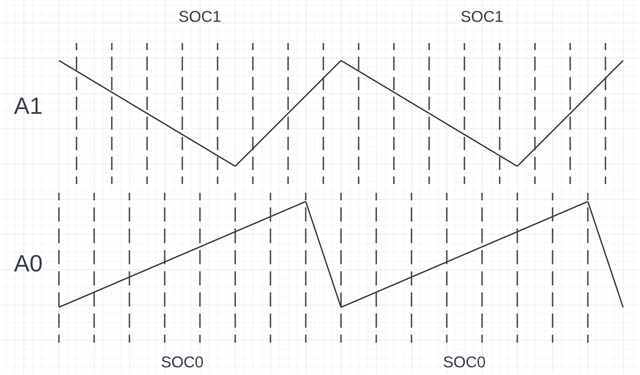

In my application, I have six analog signals, with each of the three ADCs sampling two of them, one on SOC0 and the other on SOC1. All SOCs are triggered via an ePWM (CMPC triggers EPWMxSOCA, which routes to SOC0 of each ADC, CMPD triggers EPWMxSOCB, which routes to SOC1 of each ADC). I also have my main real-time ISR which I execute every 10us. The ISR is triggered by one of the ADCINTs, and thus executes synchronously with all the ADC conversions.

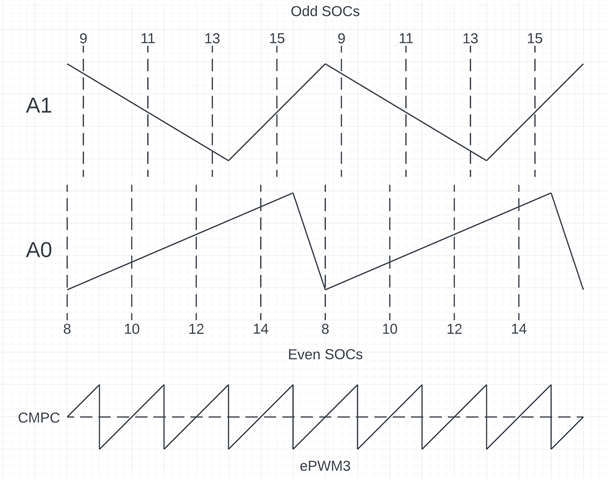

Currently this means each signal is sampled once per ISR, but I'm finding that some of the signals have significant errors, and it's apparent that this is because these signals have significant ripple on them (they measure inductor current, which has large ripple by design). Using an aggressive analog lowpass filter is not feasible because that would greatly slow down my control loop. The ripple is synchronous to my ISR and ADC conversions, so oversampling and averaging all samples each ISR should give me a good measure of average current with minimal delay. An OSR of 8 should be sufficient (each signal sampled at 800ksps, thus each ADC sampling at 1600ksps).

But I'm having trouble coming up with a way to implement the oversampling properly. Here's a few options I've considered:

1. Most e2e posts about oversampling with c2000 parts just say to assign multiple SOCs with the same trigger, and let them all convert sequentially in a burst. But that results irregular sample timing (determined by the SOCs' configurations), and for this to work properly my samples must be evenly distributed in time.

2. Use the same SOCs for all the samples and have the CLA grab each conversion and store/accumulate it in RAM. But I don't have a device with a CLA due to part availability. I already tried doing this with a nested CPU ISR, but there was far too much overhead.

3. Use separate SOCs for each conversion, and use more synchronized ePWM channels to create more SOC triggers with the appropriate timings. But I would need all eight ePWM modules dedicated for this, which I can't do.

4. Use the same SOCs for all the samples, and retrieve the samples using the DMA. Might be doable by using all six DMA channels, but I need at least one DMA channel for other purposes. I'm not so familiar with the DMA's abilities though, maybe there's a way for a DMA channel to handle more than one signal by automatically changing the source address...

I'm surprised this is turning out to be such a challenge, really wish there was a feature in the ADC to put conversions in a FIFO, or a simple accumulator...

Any ideas?