Hi expert,

I have a problem with my fast comparators. I give you a small description of my architecture: I use the TZ1 to TZ3 signals to cut my ePWMs (they correspond to driver returns) via Input_X_Bar and I use the TRIPIN4 signals etc. for overvoltage signals etc...

I use a trip zone interrupt per ePWM, this one allows me to keep an event log as well as to shut down the ePWMs.

I have linked the TZ1 to TZ3 signals in interrupt via EPWM_TZ_INTERRUPT_CBC and my CMPSS via EPWM_TZ_INTERRUPT_DCBEVT2 event.

I have a problem, I enter the interrupt at the CMPSS level as soon as my system is switched on, while all the inputs are at 0. I don't think it's a hardware problem, I've explored the forum a lot but I can't find an answer. I must have forgotten something, can you help me please?

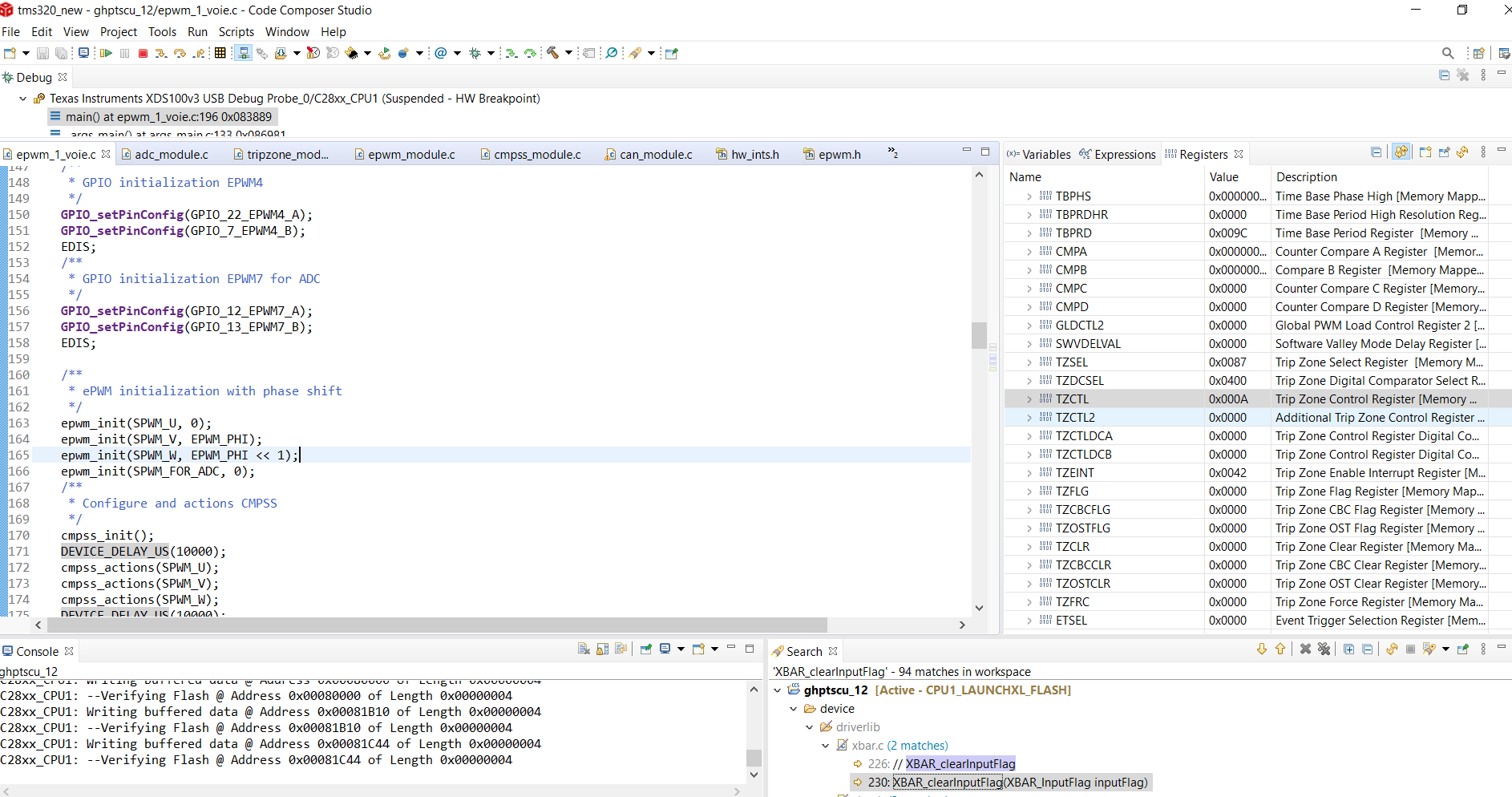

I don't go into interruption on the TZ1 or TZ2 or TZ3 if I don't want to, so I target the problem to the CMPSS. At initialization the TZFLG, TZCBCFLG and TZEINT registers are at 0, which seems to me consistent on each ePWM used. However the XBARFLG1 register is set to 1 on the configured comparators and I can't set them to 0 via the XBARCLR1 register. But it is a flag and not the source signal, I try to go up the chain but I am blocked in my reasoning.

You can see screenshots :

#include "cmpss_module.h"

#include "device.h"

#include "adc_module.h"

#include "epwm_module.h"

#include "monitoring.h"

const uint16_t THRESHOLD_MU_FUEL_CELL_PCH = 700U;

const uint16_t THRESHOLD_MU_TRAC_BATT_PCH = 950U;

const uint16_t THRESHOLD_MI_L_U = 155U;

const uint16_t THRESHOLD_MI_L_V = 155U;

const uint16_t THRESHOLD_MI_L_W = 155U;

const uint16_t THRESHOLD_MI_TRAC_BATT = 230U;

const uint16_t THRESHOLD_MT_COLD_PLATE = 120U;

uint16_t THRESHOLD_MI_L_U_DIGITAL = 0;

uint16_t THRESHOLD_MI_L_V_DIGITAL = 0;

uint16_t THRESHOLD_MI_L_W_DIGITAL = 0;

uint16_t THRESHOLD_MI_TRAC_BATT_DIGITAL = 0;

uint16_t THRESHOLD_MU_FUEL_CELL_PCH_DIGITAL = 0;

uint16_t THRESHOLD_MU_TRAC_BATT_PCH_DIGITAL = 0;

/**Comparator subsystem module initialization

See requirement REQ_SYST0030, REQ_SYST0031, REQ_SYST0035, REQ_SYST0036, REQ_SYST0037 and REQ_SYST0038*/

void cmpss_init()

{

/**Enable CMPSS and configure the negative input signal to come from the DAC*/

CMPSS_enableModule(CMPSS1_BASE);

CMPSS_enableModule(CMPSS2_BASE);

CMPSS_enableModule(CMPSS3_BASE);

CMPSS_enableModule(CMPSS4_BASE);

/**Use VDDA as the reference for the DAC and set DAC value to midpoint for arbitrary reference.*/

CMPSS_configDAC(CMPSS1_BASE, CMPSS_DACREF_VDAC);

CMPSS_configDAC(CMPSS2_BASE, CMPSS_DACREF_VDAC);

CMPSS_configDAC(CMPSS3_BASE, CMPSS_DACREF_VDAC);

CMPSS_configDAC(CMPSS4_BASE, CMPSS_DACREF_VDAC);

/**To use CMP1_HP2 pin A6 for MU_TRAC_BATT_PCH*/

ASysCtl_selectCMPHPMux(ASYSCTL_CMPHPMUX_SELECT_1, 2);

/**To use CMP1_LP3 pin A15/C7 for MU_FUEL_CELL_PCH*/

ASysCtl_selectCMPLPMux(ASYSCTL_CMPLPMUX_SELECT_1, 3);

/**To use CMP3_HP1 pin A5/C2 for MI_L_W*/

ASysCtl_selectCMPHPMux(ASYSCTL_CMPHPMUX_SELECT_3, 1);

/**To use CMP2_HP1 pin A12/C1 for MI_L_U*/

ASysCtl_selectCMPHPMux(ASYSCTL_CMPHPMUX_SELECT_2, 1);

/**To use CMP2_LP4 pin A8/C11 for MI_L_V*/

ASysCtl_selectCMPLPMux(ASYSCTL_CMPLPMUX_SELECT_2, 4);

/**To use CMP4_HP1 pin A7/C3 for MI_TRAC_BATT*/

ASysCtl_selectCMPHPMux(ASYSCTL_CMPHPMUX_SELECT_4, 1);

/**Configure the output signals. Both CTRIPH will be fed by the asynchronous comparator output.*/

///1

THRESHOLD_MU_TRAC_BATT_PCH_DIGITAL = (((THRESHOLD_MU_TRAC_BATT_PCH * 8.2 * 0.00013796) + OFFSET_AMPLI) * ADC_RESOLUTION) / FULL_SCALE;

CMPSS_configHighComparator(CMPSS1_BASE, CMPSS_INSRC_DAC); // Threshold drive by GPIO or input DAC

CMPSS_setDACValueHigh(CMPSS1_BASE, THRESHOLD_MU_TRAC_BATT_PCH_DIGITAL); // Define threshold associated

CMPSS_configOutputsHigh(CMPSS1_BASE, CMPSS_TRIP_SYNC_COMP); // Set output comparator (synchronous or asynchronous)

///2

THRESHOLD_MU_FUEL_CELL_PCH_DIGITAL = (((THRESHOLD_MU_FUEL_CELL_PCH * 8.2 * 0.00013796) + OFFSET_AMPLI) * ADC_RESOLUTION) / FULL_SCALE;

CMPSS_configLowComparator(CMPSS1_BASE, CMPSS_INSRC_DAC); // Threshold drive by GPIO or input DAC

CMPSS_setDACValueLow(CMPSS1_BASE, THRESHOLD_MU_FUEL_CELL_PCH_DIGITAL); // Define threshold associated

CMPSS_configOutputsLow(CMPSS1_BASE, CMPSS_TRIP_SYNC_COMP); // Set output comparator (synchronous or asynchronous)

/**Configure the output signals. Both CTRIPH will be fed by the asynchronous comparator output.*/

///1

THRESHOLD_MI_L_U_DIGITAL = (((THRESHOLD_MI_L_U * 0.625 / 200) + REF_MI_H_2V5_AROUND) * ADC_RESOLUTION) / FULL_SCALE;

CMPSS_configHighComparator(CMPSS2_BASE, CMPSS_INSRC_DAC); // Threshold drive by GPIO or input DAC

CMPSS_setDACValueHigh(CMPSS2_BASE, THRESHOLD_MI_L_U_DIGITAL); // Define threshold associated

CMPSS_configOutputsHigh(CMPSS2_BASE, CMPSS_TRIP_SYNC_COMP); // Set output comparator (synchronous or asynchronous)

///2

THRESHOLD_MI_L_V_DIGITAL = (((THRESHOLD_MI_L_V * 0.625 / 200) + REF_MI_H_2V5_AROUND) * ADC_RESOLUTION) / FULL_SCALE;

CMPSS_configLowComparator(CMPSS2_BASE, CMPSS_INSRC_DAC); // Threshold drive by GPIO or input DAC

CMPSS_setDACValueLow(CMPSS2_BASE, THRESHOLD_MI_L_V_DIGITAL); // Define threshold associated

CMPSS_configOutputsLow(CMPSS2_BASE, CMPSS_TRIP_SYNC_COMP); // Set output comparator (synchronous or asynchronous)

/**Configure the output signals. Both CTRIPH will be fed by the asynchronous comparator output.*/

///1

THRESHOLD_MI_L_W_DIGITAL = (((THRESHOLD_MI_L_W * 0.625 / 200) + REF_MI_H_2V5_AROUND) * ADC_RESOLUTION) / FULL_SCALE;

CMPSS_configHighComparator(CMPSS3_BASE, CMPSS_INSRC_DAC); // Threshold drive by GPIO or input DAC

CMPSS_setDACValueHigh(CMPSS3_BASE, THRESHOLD_MI_L_W_DIGITAL); // Define threshold associated

CMPSS_configOutputsHigh(CMPSS3_BASE, CMPSS_TRIP_SYNC_COMP); // Set output comparator (synchronous or asynchronous)

/**Configure the output signals. Both CTRIPH will be fed by the asynchronous comparator output.*/

///1

THRESHOLD_MI_TRAC_BATT_DIGITAL = ((((THRESHOLD_MI_TRAC_BATT * 2 * 301) / 100000) + REF_MI_BT_1V5) * ADC_RESOLUTION) / FULL_SCALE;

CMPSS_configHighComparator(CMPSS4_BASE, CMPSS_INSRC_DAC); // Threshold drive by GPIO or input DAC

CMPSS_setDACValueHigh(CMPSS4_BASE, THRESHOLD_MI_TRAC_BATT_DIGITAL); // Define threshold associated

CMPSS_configOutputsHigh(CMPSS4_BASE, CMPSS_TRIP_SYNC_COMP); // Set output comparator (synchronous or asynchronous)

/**Configure TRIP4 to be CTRIP1H using the ePWM X-BAR. Attach CMPSS output to TRIPINx via EPWMXBAR module*/

XBAR_setEPWMMuxConfig(XBAR_TRIP4, XBAR_EPWM_MUX00_CMPSS1_CTRIPH);

XBAR_setEPWMMuxConfig(XBAR_TRIP5, XBAR_EPWM_MUX01_CMPSS1_CTRIPL);

XBAR_setEPWMMuxConfig(XBAR_TRIP7, XBAR_EPWM_MUX04_CMPSS3_CTRIPH);

XBAR_setEPWMMuxConfig(XBAR_TRIP8, XBAR_EPWM_MUX02_CMPSS2_CTRIPH);

XBAR_setEPWMMuxConfig(XBAR_TRIP9, XBAR_EPWM_MUX03_CMPSS2_CTRIPL);

XBAR_setEPWMMuxConfig(XBAR_TRIP10, XBAR_EPWM_MUX06_CMPSS4_CTRIPH);

/**See the ePWM X-BAR Mux configuration table, see Crossbar(X-BAR) doc for more informations*/

XBAR_enableEPWMMux(XBAR_TRIP4, XBAR_MUX00);

XBAR_enableEPWMMux(XBAR_TRIP5, XBAR_MUX01);

XBAR_enableEPWMMux(XBAR_TRIP7, XBAR_MUX04);

XBAR_enableEPWMMux(XBAR_TRIP8, XBAR_MUX02);

XBAR_enableEPWMMux(XBAR_TRIP9, XBAR_MUX03);

XBAR_enableEPWMMux(XBAR_TRIP10, XBAR_MUX06);

}

/**Shutdown ePWM when DCBEVT2 is triggered*/

void cmpss_actions(uint32_t base)

{

/**Configure ePWMx to output low on TZx TRIP*/

EPWM_setTripZoneAction(base, EPWM_TZ_ACTION_EVENT_TZA, EPWM_TZ_ACTION_LOW);

EPWM_setTripZoneAction(base, EPWM_TZ_ACTION_EVENT_TZB, EPWM_TZ_ACTION_LOW);

/**Trigger event when DCBH is high*/

EPWM_setTripZoneDigitalCompareEventCondition(base, EPWM_TZ_DC_OUTPUT_B2, EPWM_TZ_EVENT_DCXH_HIGH);

/**Configure DCBH to use TRIPINx as an input*/

EPWM_enableDigitalCompareTripCombinationInput(base, EPWM_DC_COMBINATIONAL_TRIPIN4, EPWM_DC_TYPE_DCBH);

EPWM_enableDigitalCompareTripCombinationInput(base, EPWM_DC_COMBINATIONAL_TRIPIN5, EPWM_DC_TYPE_DCBH);

EPWM_enableDigitalCompareTripCombinationInput(base, EPWM_DC_COMBINATIONAL_TRIPIN7, EPWM_DC_TYPE_DCBH);

EPWM_enableDigitalCompareTripCombinationInput(base, EPWM_DC_COMBINATIONAL_TRIPIN8, EPWM_DC_TYPE_DCBH);

EPWM_enableDigitalCompareTripCombinationInput(base, EPWM_DC_COMBINATIONAL_TRIPIN9, EPWM_DC_TYPE_DCBH);

EPWM_enableDigitalCompareTripCombinationInput(base, EPWM_DC_COMBINATIONAL_TRIPIN10, EPWM_DC_TYPE_DCBH);

/**Enable DCB as DCBEVT2*/

EPWM_enableTripZoneSignals(base, EPWM_TZ_SIGNAL_DCBEVT2);

/**Enable interrupt*/

EPWM_enableTripZoneInterrupt(base, EPWM_TZ_INTERRUPT_DCBEVT2);

}

#include "device.h"

#include "tripzone_module.h"

#include "epwm_module.h"

#include "monitoring.h"

/**Initialize trip zone concerned by DRV signals provided from InputXbar to shutdown ePWM when signals are to low level.

See requirements REQ_SYST0022, REQ_SYST0023 and REQ_SYST0024*/

void trip_zone_config(void)

{

/**DRV-U signals to trip zone*/

GPIO_setPinConfig(GPIO_45_GPIO45);

GPIO_setDirectionMode(45, GPIO_DIR_MODE_IN);

GPIO_setPadConfig(45, GPIO_PIN_TYPE_STD);

/**DRV-V signals to trip zone*/

GPIO_setPinConfig(GPIO_5_GPIO5);

GPIO_setDirectionMode(5, GPIO_DIR_MODE_IN);

GPIO_setPadConfig(5, GPIO_PIN_TYPE_STD);

/**DRV-W signals to trip zone*/

GPIO_setPinConfig(GPIO_9_GPIO9);

GPIO_setDirectionMode(9, GPIO_DIR_MODE_IN);

GPIO_setPadConfig(9, GPIO_PIN_TYPE_STD);

XBAR_setInputPin(INPUTXBAR_BASE, XBAR_INPUT1, 45);

XBAR_setInputPin(INPUTXBAR_BASE, XBAR_INPUT2, 5);

XBAR_setInputPin(INPUTXBAR_BASE, XBAR_INPUT3, 9);

/**Enable TZx as cycle by cycle trip sources

TZ1 for DRV_U*/

EPWM_enableTripZoneSignals(SPWM_U, EPWM_TZ_SIGNAL_CBC1);

EPWM_enableTripZoneSignals(SPWM_V, EPWM_TZ_SIGNAL_CBC1);

EPWM_enableTripZoneSignals(SPWM_W, EPWM_TZ_SIGNAL_CBC1);

/**TZ2 for DRV_V*/

EPWM_enableTripZoneSignals(SPWM_U, EPWM_TZ_SIGNAL_CBC2);

EPWM_enableTripZoneSignals(SPWM_V, EPWM_TZ_SIGNAL_CBC2);

EPWM_enableTripZoneSignals(SPWM_W, EPWM_TZ_SIGNAL_CBC2);

/**TZ3 for DRV_W*/

EPWM_enableTripZoneSignals(SPWM_U, EPWM_TZ_SIGNAL_CBC3);

EPWM_enableTripZoneSignals(SPWM_V, EPWM_TZ_SIGNAL_CBC3);

EPWM_enableTripZoneSignals(SPWM_W, EPWM_TZ_SIGNAL_CBC3);

/**Action on TZx*/

EPWM_setTripZoneAction(SPWM_U, EPWM_TZ_ACTION_EVENT_TZA, EPWM_TZ_ACTION_LOW);

EPWM_setTripZoneAction(SPWM_V, EPWM_TZ_ACTION_EVENT_TZA, EPWM_TZ_ACTION_LOW);

EPWM_setTripZoneAction(SPWM_W, EPWM_TZ_ACTION_EVENT_TZA, EPWM_TZ_ACTION_LOW);

EPWM_enableTripZoneInterrupt(SPWM_U, EPWM_TZ_INTERRUPT_CBC);

EPWM_enableTripZoneInterrupt(SPWM_V, EPWM_TZ_INTERRUPT_CBC);

EPWM_enableTripZoneInterrupt(SPWM_W, EPWM_TZ_INTERRUPT_CBC);

}

/**Interrupt is trigger if CMPSS (EpWMXbar signals) are set or if DRV (InputXbar signals TZ1 à TZ3) are set.

If interrupt is trigger corresponding flag and variable state are set. And the processing of the variable is done in the state machine.*/

__interrupt void isr_trip_zone(void)

{

// Priority interrupt

// Save IER register on stack

/*volatile uint16_t tempPIEIER = HWREGH(PIECTRL_BASE + PIE_O_IER2);

// Set the global and group priority to allow CPU interrupts with higher priority

IER |= M_INT2;

IER &= MINT2;

HWREGH(PIECTRL_BASE + PIE_O_IER2) &= MG1_1;

// Enable Interrupts

Interrupt_clearACKGroup(0xFFFFU);

__asm(" NOP");

EINT;*/

/**Clear the flags, we will continue to take this interrupt until the TZ pin goes high.

In TZFLG register when interrupt is due to EpWMXbar so DCxEVTx TZFLG.DCxEVTx.bit = 1 and TZFLG.CBC.bit = 1 it's normally*/

EPWM_clearTripZoneFlag(SPWM_U, (EPWM_TZ_INTERRUPT | EPWM_TZ_FLAG_CBC | EPWM_TZ_FLAG_DCBEVT2));

EPWM_clearTripZoneFlag(SPWM_V, (EPWM_TZ_INTERRUPT | EPWM_TZ_FLAG_CBC | EPWM_TZ_FLAG_DCBEVT2));

EPWM_clearTripZoneFlag(SPWM_W, (EPWM_TZ_INTERRUPT | EPWM_TZ_FLAG_CBC | EPWM_TZ_FLAG_DCBEVT2));

/**Clear corresponding bit of interrupt source

Event log recording

See requirement REQ_SYST0032*/

if(EPWM_getCycleByCycleTripZoneFlagStatus(SPWM_U) == EPWM_TZ_CBC_FLAG_1)

{

drv_u_state = DRV_ERROR;

EPWM_clearCycleByCycleTripZoneFlag(SPWM_U ,EPWM_TZ_CBC_FLAG_1);

EPWM_clearCycleByCycleTripZoneFlag(SPWM_V ,EPWM_TZ_CBC_FLAG_1);

EPWM_clearCycleByCycleTripZoneFlag(SPWM_W ,EPWM_TZ_CBC_FLAG_1);

// Disable the interrupts to do the associated actions and not re-trigger the trip zone before the end of its processing. The interrupt will be reactivated at that time.

Interrupt_disable(INT_EPWM1_TZ);

Interrupt_disable(INT_EPWM2_TZ);

Interrupt_disable(INT_EPWM4_TZ);

}

/**See requirement REQ_SYST0033*/

else if(EPWM_getCycleByCycleTripZoneFlagStatus(SPWM_U) == EPWM_TZ_CBC_FLAG_2)

{

drv_v_state = DRV_ERROR;

EPWM_clearCycleByCycleTripZoneFlag(SPWM_U ,EPWM_TZ_CBC_FLAG_2);

EPWM_clearCycleByCycleTripZoneFlag(SPWM_V ,EPWM_TZ_CBC_FLAG_2);

EPWM_clearCycleByCycleTripZoneFlag(SPWM_W ,EPWM_TZ_CBC_FLAG_2);

// Disable the interrupts to do the associated actions and not re-trigger the trip zone before the end of its processing. The interrupt will be reactivated at that time.

Interrupt_disable(INT_EPWM1_TZ);

Interrupt_disable(INT_EPWM2_TZ);

Interrupt_disable(INT_EPWM4_TZ);

}

/**See requirement REQ_SYST0034*/

else if(EPWM_getCycleByCycleTripZoneFlagStatus(SPWM_U) == EPWM_TZ_CBC_FLAG_3)

{

drv_w_state = DRV_ERROR;

EPWM_clearCycleByCycleTripZoneFlag(SPWM_U ,EPWM_TZ_CBC_FLAG_3);

EPWM_clearCycleByCycleTripZoneFlag(SPWM_V ,EPWM_TZ_CBC_FLAG_3);

EPWM_clearCycleByCycleTripZoneFlag(SPWM_W ,EPWM_TZ_CBC_FLAG_3);

/// Disable the interrupts to do the associated actions and not re-trigger the trip zone before the end of its processing. The interrupt will be reactivated at that time.

Interrupt_disable(INT_EPWM1_TZ);

Interrupt_disable(INT_EPWM2_TZ);

Interrupt_disable(INT_EPWM4_TZ);

}

/**See requirement REQ_SYST0031*/

else if(XBAR_getInputFlagStatus(XBAR_INPUT_FLG_CMPSS1_CTRIPH) == PROTECTION_DETECTED)

{

mu_trac_batt_state = PROTECTION_DETECTED;

XBAR_clearInputFlag(XBAR_INPUT_FLG_CMPSS1_CTRIPH);

EPWM_clearCycleByCycleTripZoneFlag(SPWM_U ,EPWM_TZ_CBC_FLAG_DCBEVT2);

EPWM_clearCycleByCycleTripZoneFlag(SPWM_V ,EPWM_TZ_CBC_FLAG_DCBEVT2);

EPWM_clearCycleByCycleTripZoneFlag(SPWM_W ,EPWM_TZ_CBC_FLAG_DCBEVT2);

/// Disable the interrupts to do the associated actions and not re-trigger the trip zone before the end of its processing. The interrupt will be reactivated at that time.

Interrupt_disable(INT_EPWM1_TZ);

Interrupt_disable(INT_EPWM2_TZ);

Interrupt_disable(INT_EPWM4_TZ);

}

/**See requirement REQ_SYST0030*/

else if(XBAR_getInputFlagStatus(XBAR_INPUT_FLG_CMPSS1_CTRIPL) == PROTECTION_DETECTED)

{

mu_fuel_cell_state = PROTECTION_DETECTED;

XBAR_clearInputFlag(XBAR_INPUT_FLG_CMPSS1_CTRIPL);

EPWM_clearCycleByCycleTripZoneFlag(SPWM_U ,EPWM_TZ_CBC_FLAG_DCBEVT2);

EPWM_clearCycleByCycleTripZoneFlag(SPWM_V ,EPWM_TZ_CBC_FLAG_DCBEVT2);

EPWM_clearCycleByCycleTripZoneFlag(SPWM_W ,EPWM_TZ_CBC_FLAG_DCBEVT2);

/// Disable the interrupts to do the associated actions and not re-trigger the trip zone before the end of its processing. The interrupt will be reactivated at that time.

Interrupt_disable(INT_EPWM1_TZ);

Interrupt_disable(INT_EPWM2_TZ);

Interrupt_disable(INT_EPWM4_TZ);

}

/**See requirement REQ_SYST0035*/

else if(XBAR_getInputFlagStatus(XBAR_INPUT_FLG_CMPSS2_CTRIPH) == PROTECTION_DETECTED)

{

mi_l_u_state = PROTECTION_DETECTED;

XBAR_clearInputFlag(XBAR_INPUT_FLG_CMPSS2_CTRIPH);

EPWM_clearCycleByCycleTripZoneFlag(SPWM_U ,EPWM_TZ_CBC_FLAG_DCBEVT2);

EPWM_clearCycleByCycleTripZoneFlag(SPWM_V ,EPWM_TZ_CBC_FLAG_DCBEVT2);

EPWM_clearCycleByCycleTripZoneFlag(SPWM_W ,EPWM_TZ_CBC_FLAG_DCBEVT2);

/// Disable the interrupts to do the associated actions and not re-trigger the trip zone before the end of its processing. The interrupt will be reactivated at that time.

Interrupt_disable(INT_EPWM1_TZ);

Interrupt_disable(INT_EPWM2_TZ);

Interrupt_disable(INT_EPWM4_TZ);

}

/**See requirement REQ_SYST0036*/

else if(XBAR_getInputFlagStatus(XBAR_INPUT_FLG_CMPSS2_CTRIPL) == PROTECTION_DETECTED)

{

mi_l_v_state = PROTECTION_DETECTED;

XBAR_clearInputFlag(XBAR_INPUT_FLG_CMPSS2_CTRIPL);

EPWM_clearCycleByCycleTripZoneFlag(SPWM_U ,EPWM_TZ_CBC_FLAG_DCBEVT2);

EPWM_clearCycleByCycleTripZoneFlag(SPWM_V ,EPWM_TZ_CBC_FLAG_DCBEVT2);

EPWM_clearCycleByCycleTripZoneFlag(SPWM_W ,EPWM_TZ_CBC_FLAG_DCBEVT2);

/// Disable the interrupts to do the associated actions and not re-trigger the trip zone before the end of its processing. The interrupt will be reactivated at that time.

Interrupt_disable(INT_EPWM1_TZ);

Interrupt_disable(INT_EPWM2_TZ);

Interrupt_disable(INT_EPWM4_TZ);

}

/**See requirement REQ_SYST0037*/

else if(XBAR_getInputFlagStatus(XBAR_INPUT_FLG_CMPSS3_CTRIPH) == PROTECTION_DETECTED)

{

mi_l_w_state = PROTECTION_DETECTED;

XBAR_clearInputFlag(XBAR_INPUT_FLG_CMPSS3_CTRIPH);

EPWM_clearCycleByCycleTripZoneFlag(SPWM_U ,EPWM_TZ_CBC_FLAG_DCBEVT2);

EPWM_clearCycleByCycleTripZoneFlag(SPWM_V ,EPWM_TZ_CBC_FLAG_DCBEVT2);

EPWM_clearCycleByCycleTripZoneFlag(SPWM_W ,EPWM_TZ_CBC_FLAG_DCBEVT2);

/// Disable the interrupts to do the associated actions and not re-trigger the trip zone before the end of its processing. The interrupt will be reactivated at that time.

Interrupt_disable(INT_EPWM1_TZ);

Interrupt_disable(INT_EPWM2_TZ);

Interrupt_disable(INT_EPWM4_TZ);

}

/**See requirement REQ_SYST0038*/

else if(XBAR_getInputFlagStatus(XBAR_INPUT_FLG_CMPSS4_CTRIPH) == PROTECTION_DETECTED)

{

mi_trac_batt_state = PROTECTION_DETECTED;

XBAR_clearInputFlag(XBAR_INPUT_FLG_CMPSS4_CTRIPH);

EPWM_clearCycleByCycleTripZoneFlag(SPWM_U ,EPWM_TZ_CBC_FLAG_DCBEVT2);

EPWM_clearCycleByCycleTripZoneFlag(SPWM_V ,EPWM_TZ_CBC_FLAG_DCBEVT2);

EPWM_clearCycleByCycleTripZoneFlag(SPWM_W ,EPWM_TZ_CBC_FLAG_DCBEVT2);

/// Disable the interrupts to do the associated actions and not re-trigger the trip zone before the end of its processing. The interrupt will be reactivated at that time.

Interrupt_disable(INT_EPWM1_TZ);

Interrupt_disable(INT_EPWM2_TZ);

Interrupt_disable(INT_EPWM4_TZ);

}

/**Acknowledge this interrupt to receive more interrupts from group 2*/

Interrupt_clearACKGroup(INTERRUPT_ACK_GROUP2);

// Disable interrupts and restore registers saved:

/*DINT;

HWREGH(PIECTRL_BASE + PIE_O_IER2) = tempPIEIER;*/

}

Thanks,

Damien