Part Number: TMS320F28384S

Other Parts Discussed in Thread: C2000WARE

Hi TI,

I am trying to debug multiple cores (CPU1 and CM) on the TMS320F28384S controller but I'm having problems with debugging the connectivity Manager (CM) core. Loading the program and stepping through the code on CPU1 works perfectly everytime. However after loading the program on the CM, it goes to boot.asm instead of breaking at main. This prevents me from stepping through the CM code as there is no way of getting out of the boot.asm file. I am unable to get it to break at main and when I add breakpoints it pops up with a "all resources are in use" error.

These are the steps I'm following to try debug the CM core but with no luck.

1. Select the C28x application for debugging

2. Connect the CM

3. load symbols followed by program

When I first followed these steps it worked and it breaked at the beginning of main in the CM, but after debugging a second or third time then it stopped working and I haven't been able to get it working since.

I'm using the Blackhawk XDS200 debug probe but I was having the same problem with the XDS100 as well.

Debugging CPU1 works fine as shown below:

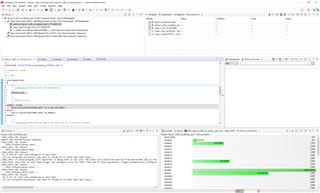

After connecting to the CM, I then load the symbols and the program (Shown in the picture below). The symbols don't seem to load correctly and I'm not sure why?

When trying to add breakpoints to the program this is the error message:

When I reset the CPU and restart the program it halts in boot.asm instead of main:

Any help or suggestions would be great?

Kind regards,

Warrick