Part Number: TMS320F2809

Other Parts Discussed in Thread: C2000WARE,

Hello,

We have a setup with the MCU I2C module configured in master mode, 380 kbps, RM=0 and is connected to some sensors.

We are still struggling to understand the ARDY and the STOP interruptions. We are planning to use them in order to know when the communication is finished. Is it the right approach? These two interruptions mean the same thing? I think I'm missing something.

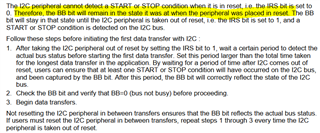

We know that when we set I2CMDR bit STP = 1 the ARDY bit from I2CSTR is not affected (below). I suppose that the ARDY interruption will not be generated, right? Please, could someone give some advice about which interruption SCD or ARDY is better to use when we need to know when the communication is finished? We have a closed loop control that will wait until the signal (from the I2C) is available to update the output. We are using FIFO interrupts to deal with the data, because our code is very time sensitive and polling data using delays is not an option.

I2CMDR bit ARDY: The registers are ready to be accessed. In the nonrepeat mode (RM = 0 in I2CMDR): If STP = 0 in I2CMDR, the ARDY bit is set when the internal data counter counts down to 0. If STP = 1, ARDY is not affected (instead, the I2C module generates a STOP condition when the counter reaches 0). In the repeat mode (RM = 1): ARDY is set at the end of each byte transmitted from I2CDXR.

Thanks,

Andrias Matheus