- Ask a related questionWhat is a related question?A related question is a question created from another question. When the related question is created, it will be automatically linked to the original question.

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

Hello,

I have some more questions about C:\ti\c2000\C2000Ware_DigitalPower_SDK_4_01_00_00\solutions\tidm_02002\f28004x\drivers\source\clllc_hal.c, lines 1534 to 1573:

I put them in the picture attached.

Please can I have answer to questions 1 to 3.

Supplementary question:

Q4) Is the isolator propagation delay mentioned in the application note represented by the variable CLLLC_pwmPhaseShiftPrimSecRef_ns?

Thank you.

Hi Kier,

Thanks for sharing your comments. I'm having your post reassigned to the reference design owner.

Regards,

Ozino

Kier, if nothing else you're certainly thorough. :)

Q1. This is the propagation delay in the PWM sync chain. it is cycle closed to be 2 cycles between each module, so to perfectly align edges an offset of 2 needs to be applied.

Q2. Yes PWM1 synco

Q3. I didn't look too closely, but my off the cuff guess would be that this is used to blank the zero crossing noise from triggering the synchronous rectification turn-off event.

Q4. I believe both Primary and secondary sides are isolated, in which case we would assume the same delay is seen by all FETs. But if there were one extra propagation delay due to isolation on the secondary side, then yes I believe it would be accounted for there.

Regards,

Cody

Many thanks for the answers Cody. Please bear with me….

On Q1), I couldn’t find mention of this propagation delay in the manual but I’ll take your word for it.

However, if the value ‘2’ is to account for the propagation delay in the synch chain, then this doesn’t seem to be applied consistency in the TI-DM 02002 code.

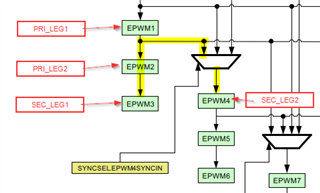

There is the following arrangement:

If there is a 2 cycle delay for every EPWM downstream of EPWM1 then surely the code should look like this:

EPWM_setPhaseShift(CLLLC_PRI_LEG2_PWM_BASE, 2);

EPWM_setPhaseShift(CLLLC_SEC_LEG1_PWM_BASE, 4);

EPWM_setPhaseShift(CLLLC_SEC_LEG2_PWM_BASE, 2);

But instead there is:

EPWM_setPhaseShift(CLLLC_SEC_LEG1_PWM_BASE, 2);

EPWM_setPhaseShift(CLLLC_SEC_LEG2_PWM_BASE, 2 );

If all four are to have in-synch TBCTR registers, then PRI_LEG2 is missing and SEC_LEG1 is not advanced enough. Is that the case?

Sorry for the pedantry but I need to understand the example thoroughly to port it across to my micro with confidence.

No problem, just joking being that I have begun recognizing your name. :)

This is a delay between sync sourcing PWM and the sync receiving PWM. Passing though an additional PWM module does not add an additional 2 cycles. My mistake for trying to be brief.

Regards,

Cody