Hi,

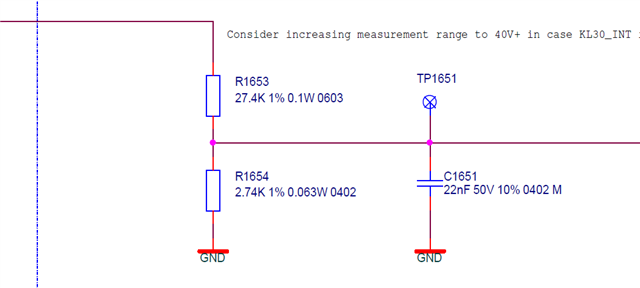

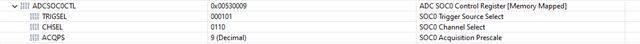

I am have an issue reading the raw values from the ADC for voltage measurement

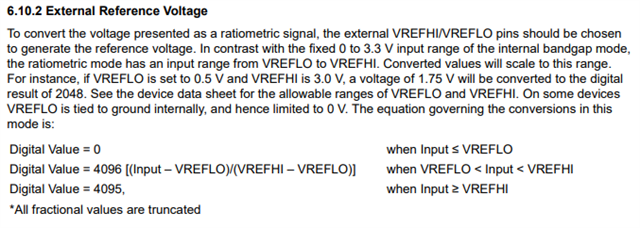

I have applied voltage 1.1V on the adc pin, and external VREFHI is 3.3V and VREFLO is grounded

So according to this formula I should I get a raw value of 1365. Although the ADC reading value is 1410

Any recommendation what could be the reason behind this?

Thank you