Other Parts Discussed in Thread: C2000WARE

Hi Experts,

Seeking your assistance:

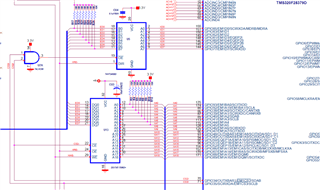

I have connected DS1747 with TMS320F28379D. I have used CS2 chip select:

Connection schematic is given below:

I have also attached sample code which I am using. I am unable to set RTC and Read RTC.

Please let me know what should be the correct address to set RTC registers.

Thank you.

Regards,

Archie A.

//#############################################################################

//

// FILE: emif_ex1_16bit_asram.c

//

// TITLE: EMIF1 ASYNC module accessing 16bit ASRAM.

//

//! \addtogroup driver_example_list

//! <h1> EMIF1 ASYNC module accessing 16bit ASRAM. </h1>

//!

//! This example configures EMIF1 in 16bit ASYNC mode and uses CS2 as chip

//! enable.

//!

//! \b External \b Connections \n

//! - External ASRAM memory (CY7C1041CV33 -10ZSXA) daughter card

//!

//! \b Watch \b Variables \n

//! - \b testStatusGlobal - Equivalent to \b TEST_PASS if test finished

//! correctly, else the value is set to \b TEST_FAIL

//! - \b errCountGlobal - Error counter

//!

//

//#############################################################################

//

// $Release Date: $

// $Copyright:

// Copyright (C) 2013-2022 Texas Instruments Incorporated - http://www.ti.com/

//

// Redistribution and use in source and binary forms, with or without

// modification, are permitted provided that the following conditions

// are met:

//

// Redistributions of source code must retain the above copyright

// notice, this list of conditions and the following disclaimer.

//

// Redistributions in binary form must reproduce the above copyright

// notice, this list of conditions and the following disclaimer in the

// documentation and/or other materials provided with the

// distribution.

//

// Neither the name of Texas Instruments Incorporated nor the names of

// its contributors may be used to endorse or promote products derived

// from this software without specific prior written permission.

//

// THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS

// "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT

// LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR

// A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT

// OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL,

// SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT

// LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE,

// DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY

// THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT

// (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE

// OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

// $

//#############################################################################

//

// Included Files

//

#include "device.h"

#include "driverlib.h"

//

// Defines

//

#define TEST_PASS 0xABCDABCD

#define TEST_FAIL 0xDEADDEAD

#define ASRAM_CS2_START_ADDR 0x100000

#define ASRAM_CS2_SIZE 0x8000

//#define RTC_RAM 0x080000 /* address ~0x0ffffe */

#define CLOCK 0x7fff0

#define YY ASRAM_CS2_START_ADDR+CLOCK+0x0f

#define MM ASRAM_CS2_START_ADDR+CLOCK+0x0e

#define DD ASRAM_CS2_START_ADDR+CLOCK+0x0d

#define DY ASRAM_CS2_START_ADDR+CLOCK+0x0c

#define HH ASRAM_CS2_START_ADDR+CLOCK+0x0b

#define MN ASRAM_CS2_START_ADDR+CLOCK+0x0a

#define SS ASRAM_CS2_START_ADDR+CLOCK+0x09

#define CONT ASRAM_CS2_START_ADDR+CLOCK+0x08

/*

#define YY *((unsigned int *) RTC_RAM+CLOCK+0x0f)

#define MM *((unsigned int *) RTC_RAM+CLOCK+0x0e)

#define DD *((unsigned int *) RTC_RAM+CLOCK+0x0d)

#define HH *((unsigned int *) RTC_RAM+CLOCK+0x0b)

#define MN *((unsigned int *) RTC_RAM+CLOCK+0x0a)

#define SS *((unsigned int *) RTC_RAM+CLOCK+0x09)

#define CONT *((unsigned int *) RTC_RAM+CLOCK+0x08)

*/

//

// Globals

//

uint16_t errCountGlobal = 0;

uint32_t testStatusGlobal;

uint32_t i;

//

// Function Prototypes

//

extern void setupEMIF1PinmuxAsync16Bit(void);

extern void setupEMIF1PinmuxAsync8Bit(void); // Added this line

uint16_t readWriteMem(uint32_t startAddr, uint32_t memSize);

uint16_t walkMemData(uint32_t startAddr, uint32_t memSize);

uint16_t walkMemAddr(uint32_t startAddr, uint32_t addrSize);

uint16_t accessMemData(uint32_t startAddr, uint32_t sizeToCheck);

//

// Main

//

void main(void)

{

//unsigned int yearvar;

uint16_t errCountLocal;

EMIF_AsyncTimingParams tparam;

testStatusGlobal = TEST_FAIL;

// yearvar=YY;

//

// Initialize device clock and peripherals.

//

Device_init();

//

// Disable all the interrupts.

//

DINT;

//

// Setup GPIO by disabling pin locks and enabling pullups.

//

Device_initGPIO();

//

// Initialize PIE and clear PIE registers. Disables CPU interrupts.

//

Interrupt_initModule();

//

// Initialize the PIE vector table with pointers to the shell Interrupt

// Service Routines (ISR).

//

Interrupt_initVectorTable();

//

// Configure to run EMIF1 on full Rate. (EMIF1CLK = CPU1SYSCLK)

//

SysCtl_setEMIF1ClockDivider(SYSCTL_EMIF1CLK_DIV_1);

//

// Grab EMIF1 For CPU1.

//

EMIF_selectMaster(EMIF1CONFIG_BASE, EMIF_MASTER_CPU1_G);

//

// Disable Access Protection. (CPU_FETCH/CPU_WR/DMA_WR)

//

EMIF_setAccessProtection(EMIF1CONFIG_BASE, 0x0);

//

// Commit the configuration related to protection. Till this bit remains

// set, contents of EMIF1ACCPROT0 register can't be changed.

//

EMIF_commitAccessConfig(EMIF1CONFIG_BASE);

//

// Lock the configuration so that EMIF1COMMIT register can't be changed

// any more.

//

EMIF_lockAccessConfig(EMIF1CONFIG_BASE);

//

// Configure GPIO pins for EMIF1.

//

// setupEMIF1PinmuxAsync16Bit(); // function commented by skg

setupEMIF1PinmuxAsync8Bit(); // function added by skg as made it for 8 bit from 16 bit

//

// Configures Normal Asynchronous Mode of Operation.

//

EMIF_setAsyncMode(EMIF1_BASE, EMIF_ASYNC_CS2_OFFSET,

EMIF_ASYNC_NORMAL_MODE);

//

// Disables Extended Wait Mode.

//

EMIF_disableAsyncExtendedWait(EMIF1_BASE, EMIF_ASYNC_CS2_OFFSET);

//

// Configure EMIF1 Data Bus Width.

//

/*

EMIF_setAsyncDataBusWidth(EMIF1_BASE, EMIF_ASYNC_CS2_OFFSET, // function commented by skg

EMIF_ASYNC_DATA_WIDTH_16);*/

EMIF_setAsyncDataBusWidth(EMIF1_BASE, EMIF_ASYNC_CS2_OFFSET, // function added by skg as changed data width from 16 to 8

EMIF_ASYNC_DATA_WIDTH_8);

//

// Configure the access timing for CS2 space.

//

/* tparam.rSetup = 0;

tparam.rStrobe = 3;

tparam.rHold = 0;

tparam.turnArnd = 0;

tparam.wSetup = 0;

tparam.wStrobe = 1;

tparam.wHold = 0;*/

tparam.rSetup = 100;

tparam.rStrobe = 100;

tparam.rHold = 20;

tparam.turnArnd = 100;

tparam.wSetup = 100;

tparam.wStrobe = 80;

tparam.wHold = 20;

EMIF_setAsyncTimingParams(EMIF1_BASE, EMIF_ASYNC_CS2_OFFSET, &tparam);

//

// Checks basic RD/WR access to CS2 space.

//

//CONT=0x80;

// YY=0x21;

// CONT=0x00;

// yearvar=YY;

while(1)

{

errCountLocal = readWriteMem(CONT, 1);

errCountGlobal = errCountGlobal + errCountLocal;

// errCountLocal = readWriteMem(ASRAM_CS2_START_ADDR, ASRAM_CS2_SIZE);

//errCountGlobal = errCountGlobal + errCountLocal;

}

//

// Address walk checks. (Tested for Memory with address width of 16bit)

//

errCountLocal = walkMemAddr(ASRAM_CS2_START_ADDR, 16);

errCountGlobal = errCountGlobal + errCountLocal;

//

// Data walk checks.

//

errCountLocal = walkMemData(ASRAM_CS2_START_ADDR, ASRAM_CS2_SIZE);

errCountGlobal = errCountGlobal + errCountLocal;

//

// Data size checks.

//

errCountLocal = accessMemData(ASRAM_CS2_START_ADDR, 4);

errCountGlobal = errCountGlobal + errCountLocal;

if(errCountGlobal == 0x0)

{

testStatusGlobal = TEST_PASS;

}

while(1);

}

//

// Read Write Memory - This function performs simple read/write word accesses

// to memory.

//

uint16_t readWriteMem(uint32_t startAddr, uint32_t memSize)

{

uint32_t memReadData;

uint32_t memWriteData;

uint32_t memReadDataHH,memReadDataMM,memReadDataSS,memReadDataMN,memReadDataDY,memReadDataCY;

uint32_t *memPtr;

uint32_t i;

memPtr = (uint32_t *)startAddr;

//

// Write data to memory.

//

memPtr=(uint32_t *)(CONT);

*memPtr = 0x80;

// memPtr= (uint32_t *)(MN);

// *memPtr=9;

// memPtr= (uint32_t *)(SS);

// *memPtr=0x85;

// *memPtr = 0x33;

memPtr=(uint32_t *)(CONT);

*memPtr=0x40;

memReadDataCY = *memPtr;

memPtr= (uint32_t *)(SS);

memReadDataSS = *memPtr;

memPtr= (uint32_t *)(MN);

memReadDataMN = *memPtr;

memPtr=(uint32_t *)(CONT);

*memPtr=0x20;

// *memPtr=05;

//memPtr=(uint32_t *)(CONT);

// memPtr= (uint32_t *)(DY);

// *memPtr=01;

//for(i = 0; i < memSize; i++)

/*{

*memPtr = memWriteData;

memPtr= (uint32_t *)(YY);

*memPtr=memWriteData=22;

memPtr= (uint32_t *)(SS);

*memPtr=5;

memPtr= (uint32_t *)(MM);

*memPtr=9;

memPtr= (uint32_t *)(MN);

*memPtr=5;

memPtr= (uint32_t *)(HH);

*memPtr=memWriteData=17;

memPtr= (uint32_t *)(CONT);

*memPtr=0x00;

//*memPtr=0x40;

// memWriteData += 0x11111111;

}*/

///

// Verify data written to memory.

//

//memWriteData = 0x21;

//memPtr = (uint32_t *)startAddr;

//while(1)

//{

// memPtr= (uint32_t *)(CONT);

/*memPtr=0x40;

memPtr = (uint32_t *)(MM);

memReadDataMM = *memPtr;

memPtr = (uint32_t *)(HH);

memReadDataHH = *memPtr;

memPtr= (uint32_t *)(MN);

memReadDataMN = *memPtr;

memPtr= (uint32_t *)(SS);

memReadDataSS = *memPtr;

memPtr= (uint32_t *)(DY);

memReadDataDY = *memPtr;

memPtr= (uint32_t *)(CONT);

memReadDataCY = *memPtr;

//for(i = 0; i < memSize; i++)

{

// memReadData = *memPtr;

// memPtr= (uint32_t *)(CONT);

// *memPtr=0x00;

if(memReadData != memWriteData)

{

// return(1);

}

//memPtr++;

// memWriteData += 0x11111111;

}

}*/

return(0);

}

//

// Walk Memory Data - This function performs a walking 0 & 1 on data lines

// for SRAM RD & WR.

//

uint16_t walkMemData(uint32_t startAddr, uint32_t memSize)

{

uint32_t sramReadData;

uint32_t sramWriteData;

uint32_t i;

uint32_t k;

uint32_t m;

uint32_t *memPtr;

uint32_t *memPtrIter;

memPtr = (uint32_t *)startAddr;

for(i = 0; i < memSize; i = i + 64)

{

for(m = 0; m < 2; m++)

{

//

// Write loop.

//

memPtrIter = memPtr;

sramWriteData = 0x01;

for(k = 0; k < 32; k++)

{

if(m == 0)

{

*memPtrIter++ = sramWriteData;

}

else

{

*memPtrIter++ = ~sramWriteData;

}

sramWriteData = sramWriteData << 1;

}

//

// Read loop.

//

memPtrIter = memPtr;

sramWriteData = 0x01;

for(k = 0; k < 32; k++)

{

sramReadData = *memPtrIter;

if(m == 1)

{

sramReadData = ~sramReadData;

}

if(sramReadData != sramWriteData)

{

return(1);

}

memPtrIter++;

sramWriteData = sramWriteData << 1;

}

}

memPtr = memPtrIter;

}

return(0);

}

//

// Walk Memory Addresses - This function performs a toggle on each address bit.

//

uint16_t walkMemAddr(uint32_t startAddr, uint32_t addrSize)

{

uint32_t sramReadData;

uint32_t sramWriteData;

uint32_t k;

uint32_t xshift;

uint32_t *memPtr;

uint32_t *memPtrIter;

memPtr = (uint32_t *)startAddr;

//

// Write loop.

//

xshift = 0x00000001;

sramWriteData = 0x00;

for(k = 0; k < addrSize; k++)

{

memPtrIter = (uint32_t *)(startAddr + xshift);

*memPtrIter = sramWriteData++;

xshift = xshift << 1;

}

//

// Read loop.

//

memPtrIter = memPtr;

xshift = 0x00000001;

sramWriteData = 0x00;

for(k = 0; k < addrSize; k++)

{

memPtrIter = (uint32_t *)(startAddr + xshift);

sramReadData = *memPtrIter;

if(sramReadData != sramWriteData)

{

return(1);

}

xshift = xshift << 1;

sramWriteData++;

}

return(0);

}

//

// Access Memory Data - This function performs different data type

// (HALFWORD/WORD) access.

//

uint16_t accessMemData(uint32_t startAddr, uint32_t sizeToCheck)

{

uint16_t memRdShort;

uint32_t memRdLong;

uint16_t memWrShort;

uint32_t memWrLong;

uint32_t i;

uint16_t *memPtrShort;

uint32_t *memPtrLong;

//

// Write short data.

//

memPtrShort = (uint16_t *)startAddr;

memWrShort = 0x0605;

for(i = 0; i < 2; i++)

{

*memPtrShort++ = memWrShort;

memWrShort += 0x0202;

}

//

// Write long data.

//

memPtrLong = (uint32_t *)memPtrShort;

memWrLong = 0x0C0B0A09;

for(i = 0; i < 2; i++)

{

*memPtrLong++ = memWrLong;

memWrLong += 0x04040404;

}

//

// Read short data.

//

memPtrShort = (uint16_t *)startAddr;

memWrShort = 0x0605;

for(i = 0; i < 6; i++)

{

memRdShort = *memPtrShort;

if(memRdShort != memWrShort)

{

return(1);

}

memPtrShort++;

memWrShort += 0x0202;

}

//

// Read long data.

//

memPtrLong = (uint32_t *)startAddr;

memWrLong = 0x08070605;

for(i = 0; i < 3; i++)

{

memRdLong = *memPtrLong;

if(memRdLong != memWrLong)

{

return(1);

}

memPtrLong++;

memWrLong += 0x04040404;

}

return(0);

}

//

// End of File

//

//#############################################################################

//

// FILE: emif_asram_pin_setup.c

//

// TITLE: Pin setup for EMIF module accessing ASRAM.

//

// This example configures pins for EMIF in ASYNC mode.

//

//

//#############################################################################

//

// $Release Date: $

// $Copyright:

// Copyright (C) 2013-2022 Texas Instruments Incorporated - http://www.ti.com/

//

// Redistribution and use in source and binary forms, with or without

// modification, are permitted provided that the following conditions

// are met:

//

// Redistributions of source code must retain the above copyright

// notice, this list of conditions and the following disclaimer.

//

// Redistributions in binary form must reproduce the above copyright

// notice, this list of conditions and the following disclaimer in the

// documentation and/or other materials provided with the

// distribution.

//

// Neither the name of Texas Instruments Incorporated nor the names of

// its contributors may be used to endorse or promote products derived

// from this software without specific prior written permission.

//

// THIS SOFTWARE IS PROVIDED BY THE COPYRIGHT HOLDERS AND CONTRIBUTORS

// "AS IS" AND ANY EXPRESS OR IMPLIED WARRANTIES, INCLUDING, BUT NOT

// LIMITED TO, THE IMPLIED WARRANTIES OF MERCHANTABILITY AND FITNESS FOR

// A PARTICULAR PURPOSE ARE DISCLAIMED. IN NO EVENT SHALL THE COPYRIGHT

// OWNER OR CONTRIBUTORS BE LIABLE FOR ANY DIRECT, INDIRECT, INCIDENTAL,

// SPECIAL, EXEMPLARY, OR CONSEQUENTIAL DAMAGES (INCLUDING, BUT NOT

// LIMITED TO, PROCUREMENT OF SUBSTITUTE GOODS OR SERVICES; LOSS OF USE,

// DATA, OR PROFITS; OR BUSINESS INTERRUPTION) HOWEVER CAUSED AND ON ANY

// THEORY OF LIABILITY, WHETHER IN CONTRACT, STRICT LIABILITY, OR TORT

// (INCLUDING NEGLIGENCE OR OTHERWISE) ARISING IN ANY WAY OUT OF THE USE

// OF THIS SOFTWARE, EVEN IF ADVISED OF THE POSSIBILITY OF SUCH DAMAGE.

// $

//#############################################################################

//

// Included Files

//

#include <stdint.h>

#include "device.h"

#include "driverlib.h"

#ifdef CPU1

//

// Function Prototypes

//

void setupEMIF1PinmuxAsync8Bit(void);

void setupEMIF1PinmuxAsync16Bit(void);

void setupEMIF1PinmuxAsync32Bit(void);

void setupEMIF2PinmuxAsync16Bit(void);

#endif

void setupEMIF1PinmuxAsync8Bit(void) // function added by skg

{

uint16_t i;

/* GPIO_setPinConfig(GPIO_28_EM1CS4N);

GPIO_setPinConfig(GPIO_29_EM1SDCKE);

GPIO_setPinConfig(GPIO_30_EM1CLK);*/

GPIO_setPinConfig(GPIO_31_EM1WEN);

/* GPIO_setPinConfig(GPIO_32_EM1CS0N);

GPIO_setPinConfig(GPIO_33_EM1RNW);*/

GPIO_setPinConfig(GPIO_34_EM1CS2N);

GPIO_setPinConfig(GPIO_35_EM1CS3N);

// GPIO_setPinConfig(GPIO_36_EM1WAIT);*/

GPIO_setPinConfig(GPIO_37_EM1OEN);

//

// Selecting address lines.

//

GPIO_setPinConfig(GPIO_38_EM1A0);

GPIO_setPinConfig(GPIO_39_EM1A1);

GPIO_setPinConfig(GPIO_40_EM1A2);

GPIO_setPinConfig(GPIO_41_EM1A3);

GPIO_setPinConfig(GPIO_44_EM1A4);

GPIO_setPinConfig(GPIO_45_EM1A5);

GPIO_setPinConfig(GPIO_46_EM1A6);

GPIO_setPinConfig(GPIO_47_EM1A7);

GPIO_setPinConfig(GPIO_48_EM1A8);

GPIO_setPinConfig(GPIO_49_EM1A9);

GPIO_setPinConfig(GPIO_50_EM1A10);

GPIO_setPinConfig(GPIO_51_EM1A11);

GPIO_setPinConfig(GPIO_52_EM1A12);

GPIO_setPinConfig(GPIO_86_EM1A13);

GPIO_setPinConfig(GPIO_87_EM1A14);

//

// Selecting data lines.

//

/* GPIO_setPinConfig(GPIO_63_EM1D21);

GPIO_setPinConfig(GPIO_64_EM1D20);

GPIO_setPinConfig(GPIO_65_EM1D19);

GPIO_setPinConfig(GPIO_66_EM1D18);

GPIO_setPinConfig(GPIO_67_EM1D17);

GPIO_setPinConfig(GPIO_68_EM1D16);

GPIO_setPinConfig(GPIO_69_EM1D15);

GPIO_setPinConfig(GPIO_70_EM1D14);

GPIO_setPinConfig(GPIO_71_EM1D13);

GPIO_setPinConfig(GPIO_72_EM1D12);

GPIO_setPinConfig(GPIO_73_EM1D11);

GPIO_setPinConfig(GPIO_74_EM1D10);

GPIO_setPinConfig(GPIO_75_EM1D9);

GPIO_setPinConfig(GPIO_76_EM1D8);*/

GPIO_setPinConfig(GPIO_77_EM1D7);

GPIO_setPinConfig(GPIO_78_EM1D6);

GPIO_setPinConfig(GPIO_79_EM1D5);

GPIO_setPinConfig(GPIO_80_EM1D4);

GPIO_setPinConfig(GPIO_81_EM1D3);

GPIO_setPinConfig(GPIO_82_EM1D2);

GPIO_setPinConfig(GPIO_83_EM1D1);

GPIO_setPinConfig(GPIO_85_EM1D0);

//

// Setting DQM and Bank Select lines.

//

/*GPIO_setPinConfig(GPIO_88_EM1DQM0);

GPIO_setPinConfig(GPIO_89_EM1DQM1);

GPIO_setPinConfig(GPIO_90_EM1DQM2);

GPIO_setPinConfig(GPIO_91_EM1DQM3);*/

GPIO_setPinConfig(GPIO_92_EM1BA1);

GPIO_setPinConfig(GPIO_93_EM1BA0);

// GPIO_setPinConfig(GPIO_94_EM1A21);

//

// Setup async mode and enable pull-ups for Data pins.

//

for(i=69; i<=85;i++)

{

if(i != 84)

{

GPIO_setPadConfig(i, GPIO_PIN_TYPE_PULLUP);

GPIO_setQualificationMode(i, GPIO_QUAL_ASYNC);

}

}

}

//

// Setup EMIF1 Pinmux Async 16Bit - This function configures pins for 16 bit

// Asynchronous EMIF1.

//

void setupEMIF1PinmuxAsync16Bit(void)

{

uint16_t i;

GPIO_setPinConfig(GPIO_28_EM1CS4N);

GPIO_setPinConfig(GPIO_29_EM1SDCKE);

GPIO_setPinConfig(GPIO_30_EM1CLK);

GPIO_setPinConfig(GPIO_31_EM1WEN);

GPIO_setPinConfig(GPIO_32_EM1CS0N);

GPIO_setPinConfig(GPIO_33_EM1RNW);

GPIO_setPinConfig(GPIO_34_EM1CS2N);

GPIO_setPinConfig(GPIO_35_EM1CS3N);

GPIO_setPinConfig(GPIO_36_EM1WAIT);

GPIO_setPinConfig(GPIO_37_EM1OEN);

//

// Selecting address lines.

//

GPIO_setPinConfig(GPIO_38_EM1A0);

GPIO_setPinConfig(GPIO_39_EM1A1);

GPIO_setPinConfig(GPIO_40_EM1A2);

GPIO_setPinConfig(GPIO_41_EM1A3);

GPIO_setPinConfig(GPIO_44_EM1A4);

GPIO_setPinConfig(GPIO_45_EM1A5);

GPIO_setPinConfig(GPIO_46_EM1A6);

GPIO_setPinConfig(GPIO_47_EM1A7);

GPIO_setPinConfig(GPIO_48_EM1A8);

GPIO_setPinConfig(GPIO_49_EM1A9);

GPIO_setPinConfig(GPIO_50_EM1A10);

GPIO_setPinConfig(GPIO_51_EM1A11);

GPIO_setPinConfig(GPIO_52_EM1A12);

GPIO_setPinConfig(GPIO_86_EM1A13);

GPIO_setPinConfig(GPIO_87_EM1A14);

//

// Selecting data lines.

//

GPIO_setPinConfig(GPIO_63_EM1D21);

GPIO_setPinConfig(GPIO_64_EM1D20);

GPIO_setPinConfig(GPIO_65_EM1D19);

GPIO_setPinConfig(GPIO_66_EM1D18);

GPIO_setPinConfig(GPIO_67_EM1D17);

GPIO_setPinConfig(GPIO_68_EM1D16);

GPIO_setPinConfig(GPIO_69_EM1D15);

GPIO_setPinConfig(GPIO_70_EM1D14);

GPIO_setPinConfig(GPIO_71_EM1D13);

GPIO_setPinConfig(GPIO_72_EM1D12);

GPIO_setPinConfig(GPIO_73_EM1D11);

GPIO_setPinConfig(GPIO_74_EM1D10);

GPIO_setPinConfig(GPIO_75_EM1D9);

GPIO_setPinConfig(GPIO_76_EM1D8);

GPIO_setPinConfig(GPIO_77_EM1D7);

GPIO_setPinConfig(GPIO_78_EM1D6);

GPIO_setPinConfig(GPIO_79_EM1D5);

GPIO_setPinConfig(GPIO_80_EM1D4);

GPIO_setPinConfig(GPIO_81_EM1D3);

GPIO_setPinConfig(GPIO_82_EM1D2);

GPIO_setPinConfig(GPIO_83_EM1D1);

GPIO_setPinConfig(GPIO_85_EM1D0);

//

// Setting DQM and Bank Select lines.

//

GPIO_setPinConfig(GPIO_88_EM1DQM0);

GPIO_setPinConfig(GPIO_89_EM1DQM1);

GPIO_setPinConfig(GPIO_90_EM1DQM2);

GPIO_setPinConfig(GPIO_91_EM1DQM3);

GPIO_setPinConfig(GPIO_92_EM1BA1);

GPIO_setPinConfig(GPIO_93_EM1BA0);

GPIO_setPinConfig(GPIO_94_EM1A21);

//

// Setup async mode and enable pull-ups for Data pins.

//

for(i=69; i<=85;i++)

{

if(i != 84)

{

GPIO_setPadConfig(i, GPIO_PIN_TYPE_PULLUP);

GPIO_setQualificationMode(i, GPIO_QUAL_ASYNC);

}

}

}

//

// Setup EMIF1 Pinmux Async 32Bit - This function configures pins for 32 bit

// Asynchronous EMIF1.

//

void setupEMIF1PinmuxAsync32Bit(void)

{

uint16_t i;

GPIO_setPinConfig(GPIO_28_EM1CS4N);

GPIO_setPinConfig(GPIO_29_EM1SDCKE);

GPIO_setPinConfig(GPIO_30_EM1CLK);

GPIO_setPinConfig(GPIO_31_EM1WEN);

GPIO_setPinConfig(GPIO_32_EM1CS0N);

GPIO_setPinConfig(GPIO_33_EM1RNW);

GPIO_setPinConfig(GPIO_34_EM1CS2N);

GPIO_setPinConfig(GPIO_35_EM1CS3N);

GPIO_setPinConfig(GPIO_36_EM1WAIT);

GPIO_setPinConfig(GPIO_37_EM1OEN);

//

// Selecting address lines.

//

GPIO_setPinConfig(GPIO_38_EM1A0);

GPIO_setPinConfig(GPIO_39_EM1A1);

GPIO_setPinConfig(GPIO_40_EM1A2);

GPIO_setPinConfig(GPIO_41_EM1A3);

GPIO_setPinConfig(GPIO_44_EM1A4);

GPIO_setPinConfig(GPIO_45_EM1A5);

GPIO_setPinConfig(GPIO_46_EM1A6);

GPIO_setPinConfig(GPIO_47_EM1A7);

GPIO_setPinConfig(GPIO_48_EM1A8);

GPIO_setPinConfig(GPIO_49_EM1A9);

GPIO_setPinConfig(GPIO_50_EM1A10);

GPIO_setPinConfig(GPIO_51_EM1A11);

GPIO_setPinConfig(GPIO_52_EM1A12);

GPIO_setPinConfig(GPIO_86_EM1A13);

GPIO_setPinConfig(GPIO_87_EM1A14);

//

// Selecting data lines.

//

GPIO_setPinConfig(GPIO_53_EM1D31);

GPIO_setPinConfig(GPIO_54_EM1D30);

GPIO_setPinConfig(GPIO_55_EM1D29);

GPIO_setPinConfig(GPIO_56_EM1D28);

GPIO_setPinConfig(GPIO_57_EM1D27);

GPIO_setPinConfig(GPIO_58_EM1D26);

GPIO_setPinConfig(GPIO_59_EM1D25);

GPIO_setPinConfig(GPIO_60_EM1D24);

GPIO_setPinConfig(GPIO_61_EM1D23);

GPIO_setPinConfig(GPIO_62_EM1D22);

GPIO_setPinConfig(GPIO_63_EM1D21);

GPIO_setPinConfig(GPIO_64_EM1D20);

GPIO_setPinConfig(GPIO_65_EM1D19);

GPIO_setPinConfig(GPIO_66_EM1D18);

GPIO_setPinConfig(GPIO_67_EM1D17);

GPIO_setPinConfig(GPIO_68_EM1D16);

GPIO_setPinConfig(GPIO_69_EM1D15);

GPIO_setPinConfig(GPIO_70_EM1D14);

GPIO_setPinConfig(GPIO_71_EM1D13);

GPIO_setPinConfig(GPIO_72_EM1D12);

GPIO_setPinConfig(GPIO_73_EM1D11);

GPIO_setPinConfig(GPIO_74_EM1D10);

GPIO_setPinConfig(GPIO_75_EM1D9);

GPIO_setPinConfig(GPIO_76_EM1D8);

GPIO_setPinConfig(GPIO_77_EM1D7);

GPIO_setPinConfig(GPIO_78_EM1D6);

GPIO_setPinConfig(GPIO_79_EM1D5);

GPIO_setPinConfig(GPIO_80_EM1D4);

GPIO_setPinConfig(GPIO_81_EM1D3);

GPIO_setPinConfig(GPIO_82_EM1D2);

GPIO_setPinConfig(GPIO_83_EM1D1);

GPIO_setPinConfig(GPIO_85_EM1D0);

//

// Setting DQM and Bank Select lines.

//

GPIO_setPinConfig(GPIO_88_EM1DQM0);

GPIO_setPinConfig(GPIO_89_EM1DQM1);

GPIO_setPinConfig(GPIO_90_EM1DQM2);

GPIO_setPinConfig(GPIO_91_EM1DQM3);

GPIO_setPinConfig(GPIO_92_EM1BA1);

GPIO_setPinConfig(GPIO_93_EM1BA0);

GPIO_setPinConfig(GPIO_94_EM1A21);

//

// Setup Async Mode for Data pins.

//

for(i=53; i<=85;i++)

{

if(i != 84)

{

GPIO_setPadConfig(i, GPIO_PIN_TYPE_PULLUP);

GPIO_setQualificationMode(i, GPIO_QUAL_ASYNC);

}

}

}

//

// Setup EMIF2 Pinmux Async 16Bit - This function configures pins for 16 bit

// Asynchronous EMIF2.

//

void setupEMIF2PinmuxAsync16Bit(void)

{

uint16_t i;

GPIO_setPinConfig(GPIO_96_EM2DQM1);

GPIO_setPinConfig(GPIO_97_EM2DQM0);

GPIO_setPinConfig(GPIO_98_EM2A0);

GPIO_setPinConfig(GPIO_99_EM2A1);

GPIO_setPinConfig(GPIO_100_EM2A2);

GPIO_setPinConfig(GPIO_101_EM2A3);

GPIO_setPinConfig(GPIO_102_EM2A4);

GPIO_setPinConfig(GPIO_103_EM2A5);

GPIO_setPinConfig(GPIO_104_EM2A6);

GPIO_setPinConfig(GPIO_105_EM2A7);

GPIO_setPinConfig(GPIO_106_EM2A8);

GPIO_setPinConfig(GPIO_107_EM2A9);

GPIO_setPinConfig(GPIO_108_EM2A10);

GPIO_setPinConfig(GPIO_109_EM2A11);

GPIO_setPinConfig(GPIO_110_EM2WAIT);

GPIO_setPinConfig(GPIO_111_EM2BA0);

GPIO_setPinConfig(GPIO_112_EM2BA1);

GPIO_setPinConfig(GPIO_113_EM2CAS);

GPIO_setPinConfig(GPIO_114_EM2RAS);

GPIO_setPinConfig(GPIO_115_EM2CS0N);

GPIO_setPinConfig(GPIO_116_EM2CS2N);

GPIO_setPinConfig(GPIO_117_EM2SDCKE);

GPIO_setPinConfig(GPIO_118_EM2CLK);

GPIO_setPinConfig(GPIO_119_EM2RNW);

GPIO_setPinConfig(GPIO_120_EM2WEN);

GPIO_setPinConfig(GPIO_121_EM2OEN);

//

// Selecting Data lines.

//

GPIO_setPinConfig(GPIO_53_EM2D15);

GPIO_setPinConfig(GPIO_54_EM2D14);

GPIO_setPinConfig(GPIO_55_EM2D13);

GPIO_setPinConfig(GPIO_56_EM2D12);

GPIO_setPinConfig(GPIO_57_EM2D11);

GPIO_setPinConfig(GPIO_58_EM2D10);

GPIO_setPinConfig(GPIO_59_EM2D9);

GPIO_setPinConfig(GPIO_60_EM2D8);

GPIO_setPinConfig(GPIO_61_EM2D7);

GPIO_setPinConfig(GPIO_62_EM2D6);

GPIO_setPinConfig(GPIO_63_EM2D5);

GPIO_setPinConfig(GPIO_64_EM2D4);

GPIO_setPinConfig(GPIO_65_EM2D3);

GPIO_setPinConfig(GPIO_66_EM2D2);

GPIO_setPinConfig(GPIO_67_EM2D1);

GPIO_setPinConfig(GPIO_68_EM2D0);

//

// Setup async mode for Data pins.

//

for(i=53; i<=68;i++)

{

GPIO_setPadConfig(i, GPIO_PIN_TYPE_PULLUP);

GPIO_setQualificationMode(i, GPIO_QUAL_ASYNC);

}

}

//

// End of File

//