Other Parts Discussed in Thread: TMDSCNCD28379D, SN74LVC3G07

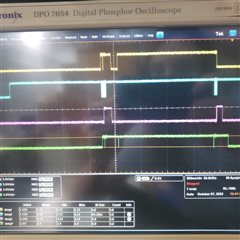

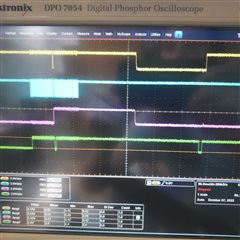

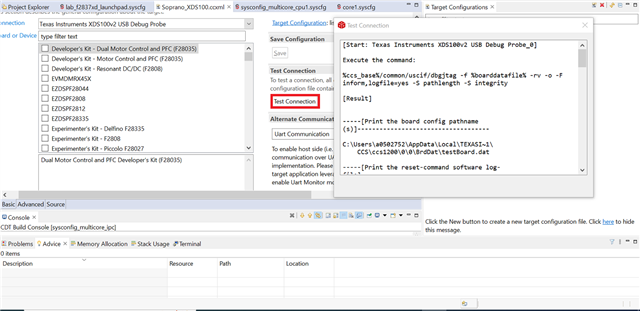

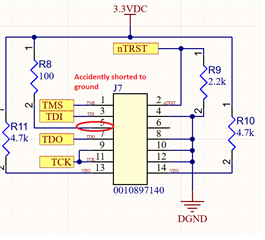

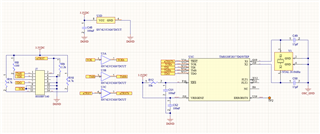

Hello, i have a TMDSCNCD28379D with a dev kit, is their anyway to manually test JTAG connection with xds100v2 black hawk that i purchased? We designed a board with a TMS320F28377DGWTEP but are having issues with our jtag programming. Attached is how we ha ve our JTAG connected to our processor if anyone can help.

ve our JTAG connected to our processor if anyone can help.