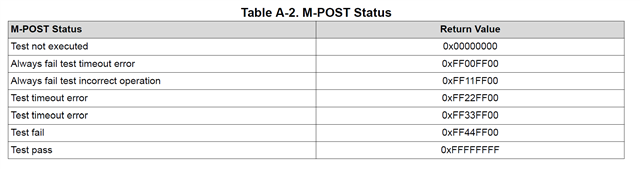

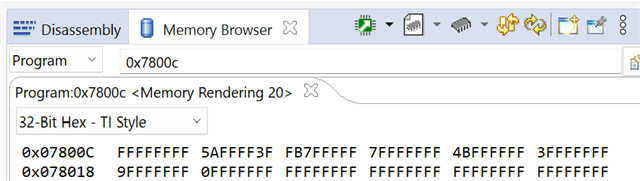

I believe I have MPOST configured to run but I continue to see 0x00000000 (Not Tested) at the result memory location. Using launch_ex1_f280025c_demo.c as the starting point I modified the source and linker files as follows to program OTP GPREG2 (0x7800E) with 0x5AFFFF3F.

#pragma DATA_SECTION (Z1_GPREG_value, "otp_z1_gpreg")

const uint64_t Z1_GPREG_value = 0x5AFFFF3FFFFFFFFF;

#pragma RETAIN(Z1_GPREG_value)

MEMORY

{

OTP_Z1_GPREG : origin = 0x0007800C, length = 0x00000004

SECTIONS

{

otp_z1_gpreg : > OTP_Z1_GPREG

After loading with the debugger, it does appear that OTP GPREG2 has been successfully programed in the Memory Browser.

The program also takes several seconds before starting which I understand is to be expected with MPOST.

However, when I look at the memory location 0x00000006 for the test result I see 0x00000000 which indicates that MPOST was not enabled.

Can you help me with what I may be doing wrong or missing?

Thanks,

Don