Hi Team,

Question 1

As shown in the figures above, the maximum sampling clock of the ADC unit is 50MHz. The system clock of the project is 200MHz, but ADCCLK = (input clock) / 2.0 configures the sampling clock of ADCC as 100MHz. Is this incorrect?

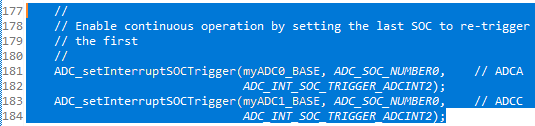

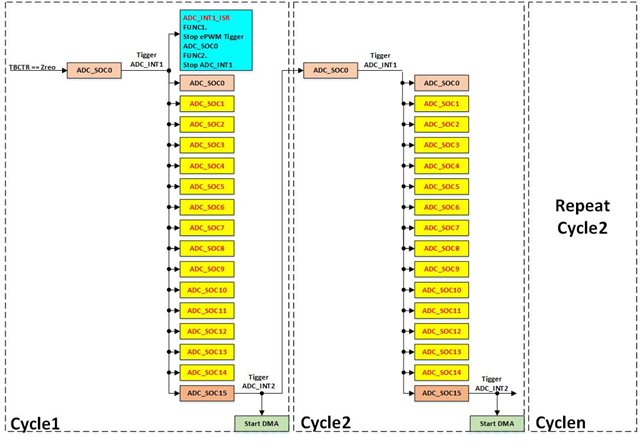

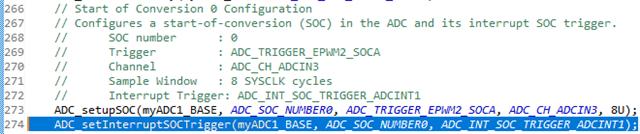

The picture above shows the ADC trigger mode of the adc_ex6_soc_continuous_dma project of 28379D that I analyzed, which does not enable ADCINT1 to trigger SOC0, but the adc_ex6_soc_continuous_dma project of 28388D in this post enables ADCINT1 to trigger SOC0, as shown in the figures below.

If it's configurated like this, I think the triggering process will be as follows.

That is to say, SOC0 is converted one more time in each cycle. Compared with the routine of 28379, there should be a problem, right?

The notes of void setupADCContinuous(uint32_t adcBase, uint16_t channel) function of 28379 clearly indicates that ADCINT1 triggers SOC1~SOC15. Could you please compare this routine of the two processors?

Kind regards,

Katherine