Other Parts Discussed in Thread: UNIFLASH, SN74HC03, SN74HC00

Contract Manufacturer here that has made a new revision of a PCB and now I am unable to program the C28 side of the CPU through the FTDI (FT2232HL) USB programmer. I can however program the M3 side without an issue AND my customer has been able to program the C28 side using a Spectrum JTAG programmer. I receive this error while trying to load flash into the C28:

Texas Instruments XDS100v2 USB Debug Probe/C28xx_0

Error connecting to the target: (Error -1015 @ 0x0) Device is not responding to the request. Device may be locked, or the debug probe connection may be unreliable. Unlock the device if possible (e.g. use wait in reset mode, and power-cycle the board). If error persists, confirm configuration and/or try more reliable JTAG settings (e.g. lower TCLK). (Emulation package 9.9.0.00040)

I have 5 boards. They all exhibit the same behavior while trying to program the C28 via the XDS100v2. I did not change the JTAG circuit at all in the PCB revision (unless there is a manufacturing issue with the boards) and this problem did not persist on the the previous boards. 3 of the new boards are using CPUs that were removed from the previous revisions board and 2 have brand new CPUs. The 3 that were removed from previous boards already were programed and the code runs but I am unable to erase or reprogram them now (C28 side).

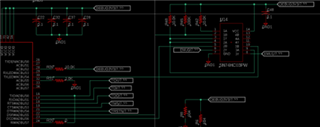

The XDS100v2 debugger is powered by the USB port and isolated from the CPU. On these new boards I did have to change the isolators from a ISO7241 to a ISO7231 b/c I could not get the ISO7241. Both are 25Mbps so I don't see why that would be the issue. I have done 'test connection' tests in Code Composer and with JP1 & JP2 on, succeed at all TCLK speeds.

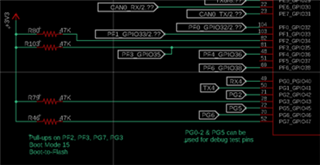

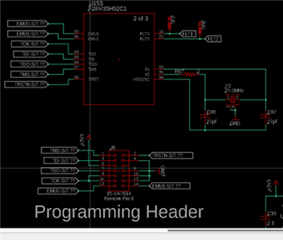

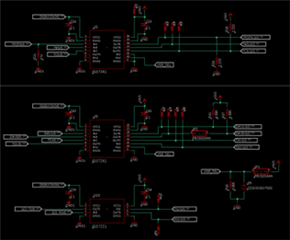

Below are the relevant parts of the schematic. The CPU is on the +3V3-GND side and the FTDI chip is on the DEBUG3V3-GND1 side. JP1 jumper is installed to program via USB and removed to program from the 14 pin JTAG header. I am not sure what the purpose of the JP2 jumper is. It is required to make one of the JTAG tests succeed but is not required to program the M3 side. CPU is set to boot in MODE 15 - Boot from Flash

My procedure for programming the boards has been to gradually increase voltage on the new board making sure all the voltage regulators work. I then plug in the USB cord, test voltages, open FTDI Prog, apply and program the XDS100 template to the FTDI chip. I then install the JP1 & JP2 jumper, open Code Composer and do a 'Connection Test' on the JTAG. I then open UniFlash and program the M3. I then try to program the C28 and get the above error. I have tried using slower TCLK down to 10kHz. I have erased the M3 and tried to program the C28 first. I have changed R41 and R67 to 2.2K (EMU pull ups) and have removed R20 (TCLK pull up).

It appears as if the JTAG connection is good from the successful connection test and being able to program the M3. I don't believe the C28 side of the CPU is bad because using a JTAG programmer it can be programmed and is running the code. What can I check or do from here?

Thanks for your help.

-

-