Other Parts Discussed in Thread: MOTORWARE

Hello,

testing through TMS320F2805x motorware example program, and save data to Flash memory during testing.

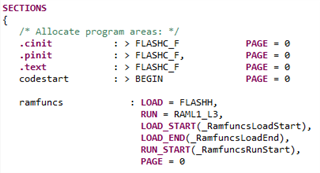

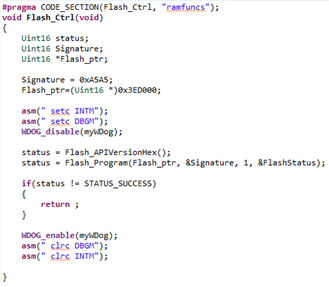

Flash memory program was implemented by referring to Flash2805x_API_Quickstart.pdf.

When running in debug mode after default settings, execution cannot be performed after calling the function below.

HAL_setParams(halHandle,&gUserParams); ===>>> PIE_setDefaultIntVectorTable(obj->pieHandle);

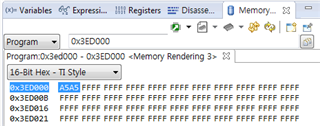

The Disassembly window after pausing debugging mode when not running is shown below.

When the PIE_setDefaultIntVectorTable() function is commented out and executed, Flash memory data writing can be checked through the Memory Browser.

The Disassembly window after pausing debugging mode when not running is shown below.

Thanks,

Seol