Other Parts Discussed in Thread: C2000WARE

Hello,

I tried to modify the C2000 built-in example "hrowm_ex1_duty_sfo_v8.c" to also enable EPWM5A by setting GPAPUD.bit.GPIO8 to 1 & setting GPAMUX1.bit.GPIO8=1(changed PWM_CH=3), it does not work, I guess the ePWM5A, GPIO8, is either NOT enable or always-low.

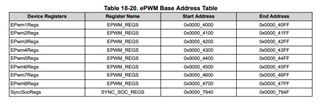

Two uncommon things: GPIO0,GPIO1(ePWM[0], ePWM[1]) are good, while I found the value of ePWM[2]=0??? So, something are wrong here. SWFSYNC=1 in ePWM[2] case, I found online explanation saying that this number should be zero, but I dont know how to fix this.