Other Parts Discussed in Thread: SYSCONFIG, CONTROLSUITE, C2000WARE

I worked through some of this problem and thought I had it solved with E2E help in this thread:

However, the problem is not solved but that ticket was marked as Resolved so I am starting a new thread. I beg pardon if that is not the correct protocol.

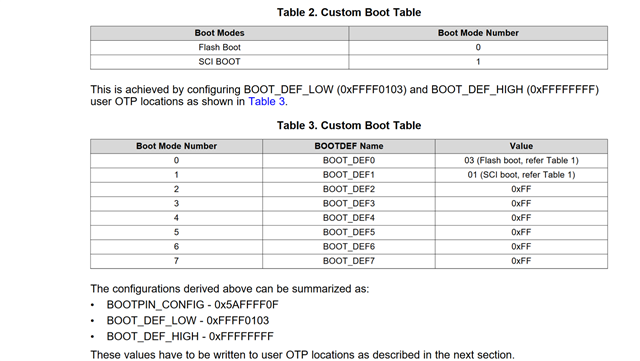

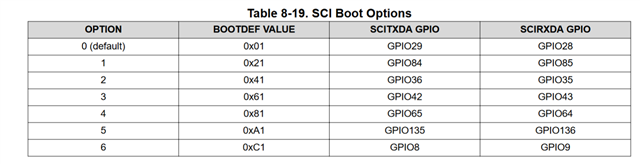

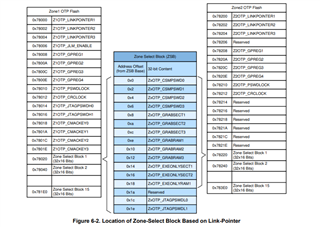

I am working from the app note SPRACN1, which is basically a variant of boot to SCIA by reading a single gpio pin. If the pin is high then SCIA boot is selected. To test the operation I have a short program that calls reset and reboots according to the boot pin state. If the input is low the program runs repeatedly, if high it stops running, from which I infer it it in SCIA boot mode. I put scope probes on the SCIA pins and started serial_flash_programmer. It is sending an 'a' but my board does not respond (I verified the port with a com terminal). Maybe the app note is missing something but I think I have the Z2 OTP setup correctly, at least it apparently changes the boot mode. My biggest suspicion (that Charles suggested earlier) is that the OTP addresses are not right.

The app code:

#include "driverlib.h"

#include "device.h"

#include "string.h"

// Per SPRACN1

#pragma RETAIN(otp_z2_data)

#pragma DATA_SECTION(otp_z2_data,"dcsm_zsel_z2_1");

const long otp_z2_data = 0x5AFFFF0F;

#pragma RETAIN(otp_z2_data_2)

#pragma DATA_SECTION(otp_z2_data_2,"dcsm_zsel_z2_2");

const long otp_z2_data_2 = 0xFFFF0103;

// End SPRACN1

void setup(void);

void scibFlush(void);

void txb(char* s);

void main(void)

{

uint32_t in = 0;

setup();

txb("\r\nStart:");

GPIO_setDirectionMode(57U, GPIO_DIR_MODE_IN);

in = GPIO_readPin(57U);

txb(in == 1 ? "\nHi" : "\nLow"); //Write to SCI B and flush.

SysCtl_resetDevice();

return 0;

}

Here are the link cmd file insertions:

MEMORY

{

PAGE 0:

DCSM_ZSEL_Z2_P0: origin = 0x078208, length = 0x000002

DCSM_ZSEL_Z2_P1: origin = 0x07820C, length = 0x000002

//DCSM_ZSEL_Z1_P0: origin = 0x07800C, length = 0x000002

//DCSM_ZSEL_Z1_P1: origin = 0x07801C, length = 0x000002

}

SECTIONS

{

dcsm_zsel_z2_1 : > DCSM_ZSEL_Z2_P0, PAGE = 0

dcsm_zsel_z2_2 : > DCSM_ZSEL_Z2_P1, PAGE = 0

}

MEMORY

{ ...