Hi Team,

There are three questions from the customer:

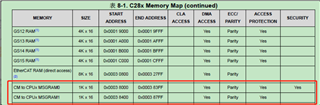

1.What difference between LS0RAM,M0RAM and D0RAM?

2.Can I put section such as .text,.bss,.stack and the other section into GSRAM? I'm not sure what the latency is.

3. I found usually program section and data section are kept separate in cmd file, is there have latency if I put program and data section in LSRAM?(I tested it with my lamp program and found it to work but not sure if it was a hidden problem)

Could you help check this case?

Thanks & Regards,

Ben