I have following queries regarding Simultaneous Sampling Mode in ADC:

1. Is there any example which I can refer for using simultaneous sampling mode of ADC

2. In the user guide, under Section 8.6: Simultaneous Sampling Mode, It is written:

Typically in an application it is expected that only the even SOCx of the pair will be used. However, it is possible

to use the odd SOCx instead, or even both. In the latter case, both SOCx triggers will start a conversion.

Therefore, caution is urged as both SOCx's will store their results to the same ADCRESULTx registers, possibly

overwriting each other.

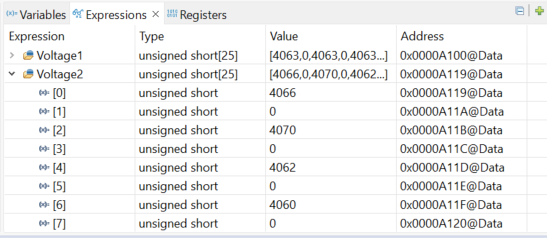

I want to use both even and odd SOCx's. I want to understand how to avoid the data overwriting in ADCRESULTx register.

User Guide Link: www.ti.com/.../spruh18i.pdf