Part Number: TMS320F280049

Hi Team,

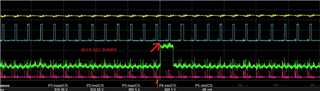

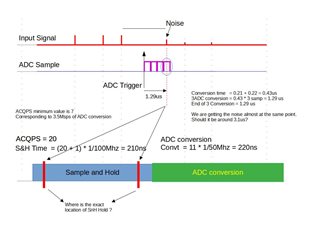

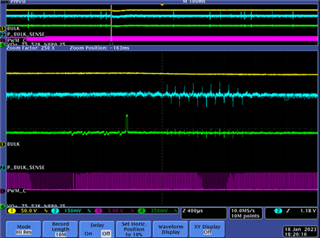

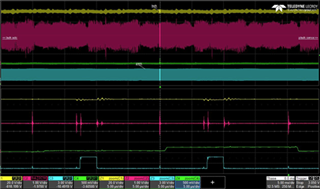

My customer is reaching out to me on a glitch that they observed on the F280049 ADC. Below is the waveform captured by customer:

Blue is the signal to the ADC, measured from MCU pin.

Green is DAC output of the same signal.

Can you share any design guides to kill the high frequency noise from SnH/ADC, if you have any.

Noise is observed in the ADCpin. But not before signal buffer.

Thanks!

BR,

Alfred