Hi,

I read some articles in the forum but i didn't get the response to my problem.

Sorry if the response is somewhere in the forum, I didn't see it.

I'm working on LaunchXL-F280049C with CCS Version: 10.1.0.00010.

I wanted to have an ADC acquisiton synchronized on raising edge of a PWM.

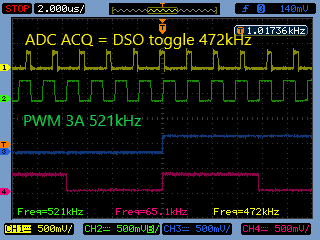

But, the ADC acquisition frequency = PWM frequency / 8

I wanted ADC acquisition frequency = PWM frequency

I don't understand why there is this factor /8.

Thanks in advance for reading this post, if anyone can help, I will be very grateful

More details are following:

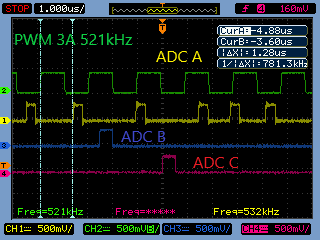

In ADC acquisition, a DSO is toggle.

The frequency of the DSO and the PWM are observed on oscilloscope.

Clock à 100MHz (checked with XCLKOUT on oscilloscope)

PWM and ADC have the same clock (see Reference Manual §3.7.5)

PWM3A is set to 521kHz (mode Up & Down) checked on oscilloscope

PWM3A is set to high level when TBCTR = 0

PWM3A is set to low level when TBCTR = TBPRD

PWM3A when TBCTR = 0 --> SOCA --> ADC A INT1

Generate the EPWMxSOCA pulse on the first event: ETPS[SOCACNT] = 0b01

I made several tests to check that ADC acquistion is well related to the frequency:

- changing PWM3A period changes DSO toggle frequency on oscilloscope as expected, but the factor /8 is still present.

- changing ETPS.SOCAPRD changes DSO toggle frequency on oscilloscope as expected, but the factor /8 is still present.

- changing ETSEL.SOCASEL shifts DSO toggle on oscilloscope, but the factor /8 is still present.

=> changing PWM3A configuration has an impact on ADC acquistion (DSO toggle frequency).

I had a look at the adc_ex2_soc_epwm example.

I don't use library function so I have compared registers between adc_ex2_soc_epwm example and my soft.

I didn't see "differences" except for the need of my software.

( In the example, I don't understand the purpose to use Counter 2 through ETPQ.SOCPSSEL = 1 and ETSOCPS.SOCAPRD2 = 1, as interrupt is once every 1 event )

(

For the need of my software: several PWM are synchronized for other ADC acquisitions:

- PWM1 (1kHz) -> PWM2 (not used) -> PWM3 (521kHz),

-> PWM4 -> PWM5 -> PWM6,

-> PWM7 -> PWM8

All PWM are synchronized on PWM1 (checked on oscilloscope)

)

The registers are following:

================================================

ClkCfgRegs

================================================

CLKCFGLOCK1 0x00000000 Lock bit for CLKCFG registers [Memory Mapped]

CLKSRCCTL1 0x00000001 Clock Source Control register-1 [Memory Mapped]

WDHALTI 0 Watchdog HALT Mode Ignore Bit

INTOSC2OFF 0 Internal Oscillator 2 Off Bit

OSCCLKSRCSEL 1 OSCCLK Source Select Bit

CLKSRCCTL2 0x00000000 Clock Source Control register-2 [Memory Mapped]

CLKSRCCTL3 0x00000002 Clock Source Control register-3 [Memory Mapped]

XCLKOUTSEL 10 XCLKOUT Source Select Bit

SYSPLLCTL1 0x00000003 SYSPLL Control register-1 [Memory Mapped]

PLLCLKEN 1 SYSPLL bypassed or included in the PLLSYSCLK path

PLLEN 1 SYSPLL enable/disable bit

SYSPLLMULT 0x00000005 SYSPLL Multiplier register [Memory Mapped]

ODIV 0 Output Clock Divider

FMULT 0 SYSPLL Fractional Multiplier

IMULT 101 SYSPLL Integer Multiplier

SYSPLLSTS 0x00000001 SYSPLL Status register [Memory Mapped]

SLIPS 0 SYSPLL Slip Status Bit

LOCKS 1 SYSPLL Lock Status Bit

SYSCLKDIVSEL 0x00000000 System Clock Divider Select register [Memory Mapped]

PLLSYSCLKDIV 0 PLLSYSCLK Divide Select

XCLKOUTDIVSEL 0x00000002 XCLKOUT Divider Select register [Memory Mapped]

XCLKOUTDIV 10 XCLKOUT Divide Select

LOSPCP 0x00000002 Low Speed Clock Source Prescalar [Memory Mapped]

LSPCLKDIV 10 LSPCLK Divide Select

MCDCR 0x00000000 Missing Clock Detect Control Register [Memory Mapped]

X1CNT 0x000003FF 10-bit Counter on X1 Clock [Memory Mapped]

CLR 0 X1 Counter Clear

X1CNT 1111111111 X1 Counter

XTALCR 0x00000000 XTAL Control Register [Memory Mapped]

================================================

AdcaRegs

================================================

ADCCTL1 0x0D84 ADC Control 1 Register [Memory Mapped]

ADCBSY 0 ADC Busy

ADCBSYCHN 1101 ADC Busy Channel

ADCPWDNZ 1 ADC Power Down

INTPULSEPOS 1 ADC Interrupt Pulse Position

ADCCTL2 0x0002 ADC Control 2 Register [Memory Mapped]

PRESCALE 10 ADC Clock Prescaler

ADCBURSTCTL 0x8109 ADC Burst Control Register [Memory Mapped]

BURSTEN 1 SOC Burst Mode Enable

BURSTSIZE 1 SOC Burst Size Select

BURSTTRIGSEL 1001 SOC Burst Trigger Source Select

ADCINTFLG 0x0000 ADC Interrupt Flag Register [Memory Mapped]

ADCINTFLGCLR 0x0000 ADC Interrupt Flag Clear Register [Memory Mapped]

ADCINTOVF 0x0000 ADC Interrupt Overflow Register [Memory Mapped]

ADCINTOVFCLR 0x0000 ADC Interrupt Overflow Clear Register [Memory Mapped]

ADCINTSEL1N2 0x0061 ADC Interrupt 1 and 2 Selection Register [Memory Mapped]

INT2CONT 0 ADCINT2 Continuous Mode Enable

INT2E 0 ADCINT2 Interrupt Enable

INT2SEL 0 ADCINT2 EOC Source Select

INT1CONT 1 ADCINT1 Continuous Mode Enable

INT1E 1 ADCINT1 Interrupt Enable

INT1SEL 1 ADCINT1 EOC Source Select

ADCINTSEL3N4 0x0000 ADC Interrupt 3 and 4 Selection Register [Memory Mapped]

ADCSOCPRICTL 0x01A0 ADC SOC Priority Control Register [Memory Mapped]

RRPOINTER 1101 Round Robin Pointer

SOCPRIORITY 0 SOC Priority

ADCINTSOCSEL1 0x0000 ADC Interrupt SOC Selection 1 Register [Memory Mapped]

ADCINTSOCSEL2 0x0000 ADC Interrupt SOC Selection 2 Register [Memory Mapped]

ADCSOCFLG1 0x0000 ADC SOC Flag 1 Register [Memory Mapped]

ADCSOCFRC1 0x0000 ADC SOC Force 1 Register [Memory Mapped]

ADCSOCOVF1 0x0000 ADC SOC Overflow 1 Register [Memory Mapped]

ADCSOCOVFCLR1 0x0000 ADC SOC Overflow Clear 1 Register [Memory Mapped]

ADCSOC0CTL 0x00920007 ADC SOC0 Control Register [Memory Mapped]

TRIGSEL 1001 SOC0 Trigger Source Select

CHSEL 100 SOC0 Channel Select

ACQPS 111 SOC0 Acquisition Prescale

ADCSOC1CTL 0x00910007 ADC SOC1 Control Register [Memory Mapped]

TRIGSEL 1001 SOC1 Trigger Source Select

CHSEL 10 SOC1 Channel Select

ACQPS 111 SOC1 Acquisition Prescale

ADCSOC2CTL 0x00000000 ADC SOC2 Control Register [Memory Mapped]

ADCSOC3CTL 0x00000000 ADC SOC3 Control Register [Memory Mapped]

ADCSOC4CTL 0x00000000 ADC SOC4 Control Register [Memory Mapped]

ADCSOC5CTL 0x00000000 ADC SOC5 Control Register [Memory Mapped]

ADCSOC6CTL 0x00000000 ADC SOC6 Control Register [Memory Mapped]

ADCSOC7CTL 0x00000000 ADC SOC7 Control Register [Memory Mapped]

ADCSOC8CTL 0x00000000 ADC SOC8 Control Register [Memory Mapped]

ADCSOC9CTL 0x00000000 ADC SOC9 Control Register [Memory Mapped]

ADCSOC10CTL 0x00000000 ADC SOC10 Control Register [Memory Mapped]

ADCSOC11CTL 0x00000000 ADC SOC11 Control Register [Memory Mapped]

ADCSOC12CTL 0x00000000 ADC SOC12 Control Register [Memory Mapped]

ADCSOC13CTL 0x00000000 ADC SOC13 Control Register [Memory Mapped]

ADCSOC14CTL 0x00000000 ADC SOC14 Control Register [Memory Mapped]

ADCSOC15CTL 0x00000000 ADC SOC15 Control Register [Memory Mapped]

ADCEVTSTAT 0x1111 ADC Event Status Register [Memory Mapped]

PPB4ZERO 0 Post Processing Block 4 Zero Crossing Flag

PPB4TRIPLO 0 Post Processing Block 4 Trip Low Flag

PPB4TRIPHI 1 Post Processing Block 4 Trip High Flag

PPB3ZERO 0 Post Processing Block 3 Zero Crossing Flag

PPB3TRIPLO 0 Post Processing Block 3 Trip Low Flag

PPB3TRIPHI 1 Post Processing Block 3 Trip High Flag

PPB2ZERO 0 Post Processing Block 2 Zero Crossing Flag

PPB2TRIPLO 0 Post Processing Block 2 Trip Low Flag

PPB2TRIPHI 1 Post Processing Block 2 Trip High Flag

PPB1ZERO 0 Post Processing Block 1 Zero Crossing Flag

PPB1TRIPLO 0 Post Processing Block 1 Trip Low Flag

PPB1TRIPHI 1 Post Processing Block 1 Trip High Flag

ADCEVTCLR 0x0000 ADC Event Clear Register [Memory Mapped]

ADCEVTSEL 0x0000 ADC Event Selection Register [Memory Mapped]

ADCEVTINTSEL 0x0000 ADC Event Interrupt Selection Register [Memory Mapped]

ADCOSDETECT 0x0000 ADC Open and Shorts Detect Register [Memory Mapped]

ADCCOUNTER 0x0191 ADC Counter Register [Memory Mapped]

FREECOUNT 110010001 ADC Free Running Counter Value

ADCREV 0x0005 ADC Revision Register [Memory Mapped]

REV 0 ADC Revision

TYPE 101 ADC Type

ADCOFFTRIM 0x0000 ADC Offset Trim Register [Memory Mapped]

OFFTRIM 0 ADC Offset Trim

ADCPPB1CONFIG 0x0000 ADC PPB1 Config Register [Memory Mapped]

ADCPPB1STAMP 0x0002 ADC PPB1 Sample Delay Time Stamp Register [Memory Mapped]

DLYSTAMP 10 ADC Post Processing Block 1 Delay Time Stamp

ADCPPB1OFFCAL 0x0000 ADC PPB1 Offset Calibration Register [Memory Mapped]

ADCPPB1OFFREF 0x0000 ADC PPB1 Offset Reference Register [Memory Mapped]

ADCPPB1TRIPHI 0x00000000 ADC PPB1 Trip High Register [Memory Mapped]

ADCPPB1TRIPLO 0x6DB00000 ADC PPB1 Trip Low/Trigger Time Stamp Register [Memory Mapped]

REQSTAMP 11011011011 ADC Post Processing Block 1 Request Time Stamp

LSIGN 0 Low Limit Sign Bit

LIMITLO 0 ADC Post Processing Block 1 Trip Low Limit

ADCPPB2CONFIG 0x0000 ADC PPB2 Config Register [Memory Mapped]

ADCPPB2STAMP 0x0002 ADC PPB2 Sample Delay Time Stamp Register [Memory Mapped]

DLYSTAMP 10 ADC Post Processing Block 2 Delay Time Stamp

ADCPPB2OFFCAL 0x0000 ADC PPB2 Offset Calibration Register [Memory Mapped]

ADCPPB2OFFREF 0x0000 ADC PPB2 Offset Reference Register [Memory Mapped]

ADCPPB2TRIPHI 0x00000000 ADC PPB2 Trip High Register [Memory Mapped]

ADCPPB2TRIPLO 0x6DB00000 ADC PPB2 Trip Low/Trigger Time Stamp Register [Memory Mapped]

REQSTAMP 11011011011 ADC Post Processing Block 2 Request Time Stamp

LSIGN 0 Low Limit Sign Bit

LIMITLO 0 ADC Post Processing Block 2 Trip Low Limit

ADCPPB3CONFIG 0x0000 ADC PPB3 Config Register [Memory Mapped]

ADCPPB3STAMP 0x0002 ADC PPB3 Sample Delay Time Stamp Register [Memory Mapped]

DLYSTAMP 10 ADC Post Processing Block 3 Delay Time Stamp

ADCPPB3OFFCAL 0x0000 ADC PPB3 Offset Calibration Register [Memory Mapped]

ADCPPB3OFFREF 0x0000 ADC PPB3 Offset Reference Register [Memory Mapped]

ADCPPB3TRIPHI 0x00000000 ADC PPB3 Trip High Register [Memory Mapped]

ADCPPB3TRIPLO 0x6DB00000 ADC PPB3 Trip Low/Trigger Time Stamp Register [Memory Mapped]

REQSTAMP 11011011011 ADC Post Processing Block 3 Request Time Stamp

LSIGN 0 Low Limit Sign Bit

LIMITLO 0 ADC Post Processing Block 3 Trip Low Limit

ADCPPB4CONFIG 0x0000 ADC PPB4 Config Register [Memory Mapped]

ADCPPB4STAMP 0x0002 ADC PPB4 Sample Delay Time Stamp Register [Memory Mapped]

DLYSTAMP 10 ADC Post Processing Block 4 Delay Time Stamp

ADCPPB4OFFCAL 0x0000 ADC PPB4 Offset Calibration Register [Memory Mapped]

ADCPPB4OFFREF 0x0000 ADC PPB4 Offset Reference Register [Memory Mapped]

ADCPPB4TRIPHI 0x00000000 ADC PPB4 Trip High Register [Memory Mapped]

ADCPPB4TRIPLO 0x6DB00000 ADC PPB4 Trip Low/Trigger Time Stamp Register [Memory Mapped]

REQSTAMP 11011011011 ADC Post Processing Block 4 Request Time Stamp

LSIGN 0 Low Limit Sign Bit

LIMITLO 0 ADC Post Processing Block 4 Trip Low Limit

ADCINTCYCLE 0x0000 ADC Early Interrupt Generation Cycle [Memory Mapped]

ADCINLTRIM1 0x00000000 ADC Linearity Trim 1 Register [Memory Mapped]

ADCINLTRIM2 0x00000000 ADC Linearity Trim 2 Register [Memory Mapped]

INLTRIM63TO32 0 ADC Linearity Trim Bits 63-32

ADCINLTRIM3 0x00000000 ADC Linearity Trim 3 Register [Memory Mapped]

INLTRIM95TO64 0 ADC Linearity Trim Bits 95-64

================================================

EPwm3Regs

================================================

TBCTL 0x2006 Time Base Control Register [Memory Mapped]

FREE_SOFT 0 Emulation Mode Bits

PHSDIR 1 Phase Direction Bit

CLKDIV 0 Time Base Clock Pre-scaler

HSPCLKDIV 0 High Speed TBCLK Pre-scaler

SWFSYNC 0 Software Force Sync Pulse

SYNCOSEL 0 Sync Output Select

PRDLD 0 Active Period Load

PHSEN 1 Phase Load Enable

CTRMODE 10 Counter Mode

TBCTL2 0x0000 Time Base Control Register 2 [Memory Mapped]

TBCTR 0x000D Time Base Counter Register [Memory Mapped]

TBCTR 1101 Counter Value

TBSTS 0x0002 Time Base Status Register [Memory Mapped]

CTRMAX 0 Counter Max Latched Status

SYNCI 1 External Input Sync Status

CTRDIR 0 Counter Direction Status

CMPCTL 0x0000 Counter Compare Control Register [Memory Mapped]

CMPCTL2 0x0000 Counter Compare Control Register 2 [Memory Mapped]

DBCTL 0x0000 Dead-Band Generator Control Register [Memory Mapped]

DBCTL2 0x0000 Dead-Band Generator Control Register 2 [Memory Mapped]

AQCTL 0x0000 Action Qualifier Control Register [Memory Mapped]

AQTSRCSEL 0x0000 Action Qualifier Trigger Event Source Select Register [Memory Mapped]

PCCTL 0x0000 PWM Chopper Control Register [Memory Mapped]

VCAPCTL 0x0000 Valley Capture Control Register [Memory Mapped]

VCNTCFG 0x0000 Valley Counter Config Register [Memory Mapped]

HRCNFG 0x0000 HRPWM Configuration Register [Memory Mapped]

HRPWR 0x0000 HRPWM Power Register [Memory Mapped]

HRMSTEP 0x0000 HRPWM MEP Step Register [Memory Mapped]

HRCNFG2 0x0000 HRPWM Configuration 2 Register [Memory Mapped]

HRPCTL 0x0000 High Resolution Period Control Register [Memory Mapped]

TRREM 0x0000 Translator High Resolution Remainder Register [Memory Mapped]

GLDCTL 0x0000 Global PWM Load Control Register [Memory Mapped]

GLDCFG 0x0000 Global PWM Load Config Register [Memory Mapped]

EPWMXLINK 0x20022222 EPWMx Link Register [Memory Mapped]

GLDCTL2LINK 10 GLDCTL2 Link

CMPDLINK 10 CMPD Link

CMPCLINK 10 CMPC Link

CMPBLINK 10 CMPB:CMPBHR Link

CMPALINK 10 CMPA:CMPAHR Link

TBPRDLINK 10 TBPRD:TBPRDHR Link

AQCTLA 0x0006 Action Qualifier Control Register For Output A [Memory Mapped]

CBD 0 Action Counter = Compare B Down

CBU 0 Action Counter = Compare B Up

CAD 0 Action Counter = Compare A Down

CAU 0 Action Counter = Compare A Up

PRD 1 Action Counter = Period

ZRO 10 Action Counter = Zero

AQCTLA2 0x0000 Additional Action Qualifier Control Register For Output A [Memory Mapped]

AQCTLB 0x0600 Action Qualifier Control Register For Output B [Memory Mapped]

CBD 1 Action Counter = Compare B Down

CBU 10 Action Counter = Compare B Up

CAD 0 Action Counter = Compare A Down

CAU 0 Action Counter = Compare A Up

PRD 0 Action Counter = Period

ZRO 0 Action Counter = Zero

AQCTLB2 0x0000 Additional Action Qualifier Control Register For Output B [Memory Mapped]

AQSFRC 0x0000 Action Qualifier Software Force Register [Memory Mapped]

AQCSFRC 0x0000 Action Qualifier Continuous S/W Force Register [Memory Mapped]

DBREDHR 0x0000 Dead-Band Generator Rising Edge Delay High Resolution Mirror Register [Memory Mapped]

DBRED 0x0000 Dead-Band Generator Rising Edge Delay High Resolution Mirror Register [Memory Mapped]

DBFEDHR 0x0000 Dead-Band Generator Falling Edge Delay High Resolution Register [Memory Mapped]

DBFED 0x0000 Dead-Band Generator Falling Edge Delay Count Register [Memory Mapped]

TBPHS 0x00000000 Time Base Phase High [Memory Mapped]

TBPRDHR 0x0000 Time Base Period High Resolution Register [Memory Mapped]

TBPRD 0x0060 Time Base Period Register [Memory Mapped]

TBPRD 96 (Decimal)

CMPA 0x00300000 Counter Compare A Register [Memory Mapped]

CMPA 48 (Decimal) Compare A Register

CMPAHR 0 (Decimal) Compare A HRPWM Extension Register

CMPB 0x00300000 Compare B Register [Memory Mapped]

CMPB 48 (Decimal) Compare B Register

CMPBHR 0 (Decimal) Compare B High Resolution Bits

CMPC 0x0000 Counter Compare C Register [Memory Mapped]

CMPD 0x0000 Counter Compare D Register [Memory Mapped]

GLDCTL2 0x0000 Global PWM Load Control Register 2 [Memory Mapped]

SWVDELVAL 0x0000 Software Valley Mode Delay Register [Memory Mapped]

TZSEL 0x0000 Trip Zone Select Register [Memory Mapped]

TZDCSEL 0x0000 Trip Zone Digital Comparator Select Register [Memory Mapped]

TZCTL 0x0000 Trip Zone Control Register [Memory Mapped]

TZCTL2 0x0000 Additional Trip Zone Control Register [Memory Mapped]

TZCTLDCA 0x0000 Trip Zone Control Register Digital Compare A [Memory Mapped]

TZCTLDCB 0x0000 Trip Zone Control Register Digital Compare B [Memory Mapped]

TZEINT 0x0000 Trip Zone Enable Interrupt Register [Memory Mapped]

TZFLG 0x0000 Trip Zone Flag Register [Memory Mapped]

TZCBCFLG 0x0000 Trip Zone CBC Flag Register [Memory Mapped]

TZOSTFLG 0x0000 Trip Zone OST Flag Register [Memory Mapped]

TZCLR 0x0000 Trip Zone Clear Register [Memory Mapped]

TZCBCCLR 0x0000 Trip Zone CBC Clear Register [Memory Mapped]

TZOSTCLR 0x0000 Trip Zone OST Clear Register [Memory Mapped]

TZFRC 0x0000 Trip Zone Force Register [Memory Mapped]

ETSEL 0x0900 Event Trigger Selection Register [Memory Mapped]

SOCBEN 0 Start of Conversion B Enable

SOCBSEL 0 Start of Conversion B Select

SOCAEN 1 Start of Conversion A Enable

SOCASEL 1 Start of Conversion A Select

INTSELCMP 0 EPWMxINT Compare Select

SOCBSELCMP 0 EPWMxSOCB Compare Select

SOCASELCMP 0 EPWMxSOCA Compare Select

INTEN 0 EPWMxINTn Enable

INTSEL 0 EPWMxINTn Select

ETPS 0x0100 Event Trigger Pre-Scale Register [Memory Mapped]

SOCBCNT 0 EPWMxSOCB Counter

SOCBPRD 0 EPWMxSOCB Period Select

SOCACNT 0 EPWMxSOCA Counter Register

SOCAPRD 1 EPWMxSOCA Period Select

SOCPSSEL 0 EPWMxSOC A/B Pre-Scale Selection Bits

INTPSSEL 0 EPWMxINTn Pre-Scale Selection Bits

INTCNT 0 EPWMxINTn Counter Register

INTPRD 0 EPWMxINTn Period Select

ETFLG 0x0004 Event Trigger Flag Register [Memory Mapped]

ETCLR 0x0000 Event Trigger Clear Register [Memory Mapped]

ETFRC 0x0000 Event Trigger Force Register [Memory Mapped]

ETINTPS 0x0000 Event-Trigger Interrupt Pre-Scale Register [Memory Mapped]

ETSOCPS 0x0000 Event-Trigger SOC Pre-Scale Register [Memory Mapped]

SOCBCNT2 0

SOCBPRD2 0

SOCACNT2 0

SOCAPRD2 0

ETCNTINITCTL 0x0000 Event-Trigger Counter Initialization Control Register [Memory Mapped]

ETCNTINIT 0x0000 Event-Trigger Counter Initialization Register [Memory Mapped]

DCTRIPSEL 0x0000 Digital Compare Trip Select Register [Memory Mapped]

DCACTL 0x0000 Digital Compare A Control Register [Memory Mapped]

DCBCTL 0x0000 Digital Compare B Control Register [Memory Mapped]

DCFCTL 0x0000 Digital Compare Filter Control Register [Memory Mapped]

DCCAPCTL 0x0000 Digital Compare Capture Control Register [Memory Mapped]

DCFOFFSET 0x0000 Digital Compare Filter Offset Register [Memory Mapped]

DCFOFFSETCNT 0x0000 Digital Compare Filter Offset Counter Register [Memory Mapped]

DCFWINDOW 0x0000 Digital Compare Filter Window Register [Memory Mapped]

DCFWINDOWCNT 0x0000 Digital Compare Filter Window Counter Register [Memory Mapped]

DCCAP 0x0000 Digital Compare Counter Capture Register [Memory Mapped]

DCAHTRIPSEL 0x0000 Digital Compare AH Trip Select [Memory Mapped]

DCALTRIPSEL 0x0000 Digital Compare AL Trip Select [Memory Mapped]

DCBHTRIPSEL 0x0000 Digital Compare BH Trip Select [Memory Mapped]

DCBLTRIPSEL 0x0000 Digital Compare BL Trip Select [Memory Mapped]

EPWMLOCK 0x00000000 EPWM Lock Register [Memory Mapped]

HWVDELVAL 0x0000 Hardware Valley Mode Delay Register [Memory Mapped]

VCNTVAL 0x0000 Hardware Valley Counter Register [Memory Mapped]

================================================

PieCtrlRegs

================================================

PIECTRL 0x0D41 ePIE Control Register [Memory Mapped]

PIEVECT 11010100000

ENPIE 1

PIEACK 0x0000 Interrupt Acknowledge Register [Memory Mapped]

PIEIER1 0x0001 Interrupt Group 1 Enable Register [Memory Mapped]

INTx16 0

INTx15 0

INTx14 0

INTx13 0

INTx12 0

INTx11 0

INTx10 0

INTx9 0

INTx8 0

INTx7 0

INTx6 0

INTx5 0

INTx4 0

INTx3 0

INTx2 0

INTx1 1

PIEIFR1 0x0004 Interrupt Group 1 Flag Register [Memory Mapped]

PIEIER2 0x0000 Interrupt Group 2 Enable Register [Memory Mapped]

PIEIFR2 0x0000 Interrupt Group 2 Flag Register [Memory Mapped]

PIEIER3 0x0000 Interrupt Group 3 Enable Register [Memory Mapped]

PIEIFR3 0x0001 Interrupt Group 3 Flag Register [Memory Mapped]

PIEIER4 0x0000 Interrupt Group 4 Enable Register [Memory Mapped]

PIEIFR4 0x0000 Interrupt Group 4 Flag Register [Memory Mapped]

PIEIER5 0x0000 Interrupt Group 5 Enable Register [Memory Mapped]

PIEIFR5 0x0000 Interrupt Group 5 Flag Register [Memory Mapped]

PIEIER6 0x0000 Interrupt Group 6 Enable Register [Memory Mapped]

PIEIFR6 0x0000 Interrupt Group 6 Flag Register [Memory Mapped]

PIEIER7 0x0000 Interrupt Group 7 Enable Register [Memory Mapped]

PIEIFR7 0x0000 Interrupt Group 7 Flag Register [Memory Mapped]

PIEIER8 0x0000 Interrupt Group 8 Enable Register [Memory Mapped]

PIEIFR8 0x0000 Interrupt Group 8 Flag Register [Memory Mapped]

PIEIER9 0x0000 Interrupt Group 9 Enable Register [Memory Mapped]

PIEIFR9 0x0000 Interrupt Group 9 Flag Register [Memory Mapped]

PIEIER10 0x0000 Interrupt Group 10 Enable Register [Memory Mapped]

PIEIFR10 0x0020 Interrupt Group 10 Flag Register [Memory Mapped]

PIEIER11 0x0000 Interrupt Group 11 Enable Register [Memory Mapped]

PIEIFR11 0x0000 Interrupt Group 11 Flag Register [Memory Mapped]

PIEIER12 0x0000 Interrupt Group 12 Enable Register [Memory Mapped]

PIEIFR12 0x0000 Interrupt Group 12 Flag Register [Memory Mapped]

================================================

SyncSocRegs

================================================

SYNCSELECT 0xE003FFC0 Sync Input and Output Select Register [Memory Mapped]

EPWM1SYNCIN 111 Selects Sync Input Source for EPWM1

SYNCOUT 0 Select Syncout Source

ECAP6SYNCIN 111 Selects Sync Input Source for ECAP6

ECAP4SYNCIN 111 Selects Sync Input Source for ECAP4

ECAP1SYNCIN 111 Selects Sync Input Source for ECAP1

EPWM7SYNCIN 0 Selects Sync Input Source for EPWM7

EPWM4SYNCIN 0 Selects Sync Input Source for EPWM4

ADCSOCOUTSELECT 0x00000000 External ADCSOC Select Register [Memory Mapped]

SYNCSOCLOCK 0x00000001 SYNCSEL and EXTADCSOC Select Lock register [Memory Mapped]

ADCSOCOUTSELECT 0 ADCSOCOUTSELECT Register Lock bit

SYNCSELECT 1 SYNCSEL Register Lock bit