Hi Team,

Can you please help with the inquiry below?

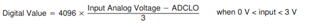

I am applying a 2V signal to ADCINA5. I connected ADCLO to ground. According to the formula below, I am expecting an approximate digital value of 2731. 4096 * [(2-0)/3] = 2731

However, this is not the result I am observing. I am reading the results using the expressions window in Code Composer Studio v5.5.0. The resulting expression is ADCRESULT5 and its value is 17040. ADCRESULT5 is then shifted to the right by 4 bits and set equal to ADC_o6 which is the expression that would be used throughout the rest of the complied code. It has a value of 1065, far from the expected digital value of 2731.

Trying other ADC inputs still results in the observed digital value not matching the theoretical digital value. Changing the input voltage also does not change the values observed in the expressions window. My understanding of ADCLO and ADCREFIN is lacking, so perhaps something is not grounded or referenced properly?

Thank you kindly,

Marvin