Other Parts Discussed in Thread: TMDSDOCK28335

Hi team,

I help my customer to ask a question.

"

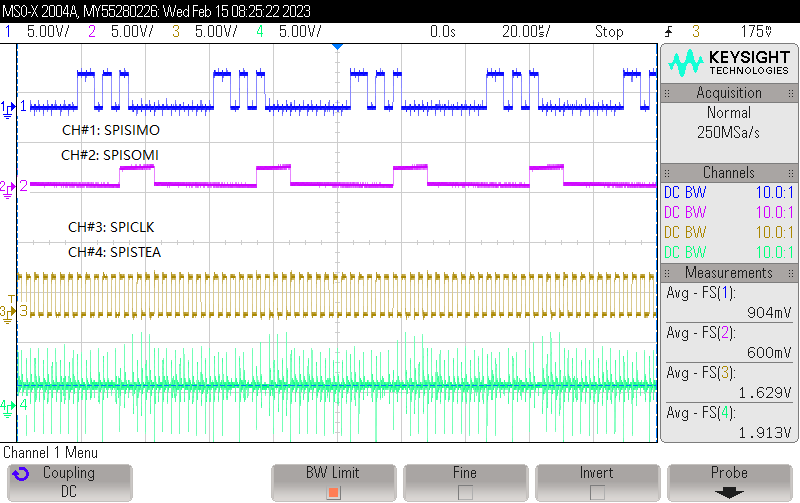

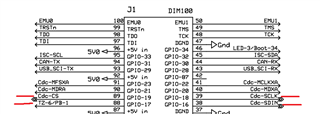

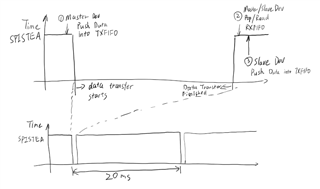

I am trying to get started with the SPI function on F28335. Right now, I am using two TMDSCNCD28335 control cards with docking stations. As I am trying to start, I am planning to use board 1 as the master device in SPI, and use board 2 as the slave device. Device 1 will send the time data with the second unit to device 2. Device 2 will only send the dummy data of 0xF to device 1. For my dissertation project, I am using the ADC interrupt triggered by EPWMSOCA instead of the SPI interrupts. I modified the demo code from the control suite to achieve this task. But it looks the data received by device 1/2 are all random values instead of the value I loaded into transmitter buffers. Here is my partial code for SPI:

DEVICE #1

void InitSpiFifoMaster() { /*Initializa SPI Slave Mode without FIFO*/ SpiaRegs.SPICCR.bit.SPISWRESET = 0; // Reset SPI SpiaRegs.SPICCR.bit.SPICHAR = 0xF; // Set SPI charater length to be 16-bit (0xF) SpiaRegs.SPICTL.bit.MASTER_SLAVE = 1; // Master->1, Slave->0 SpiaRegs.SPICTL.bit.TALK = 1; // Transmit Enable. Set as 0 will disable TX for next word by set output line HIGH SpiaRegs.SPIBRR = 0x0063; // Set baud rate: 40MHz/(0x63+0x1)=40MHz/100=400bps SpiaRegs.SPIPRI.bit.FREE = 1; // Enable Free Run, continure SPI operation no matter the suspend occurred /*Set SPI FIFO Regs*/ SpiaRegs.SPIFFTX.bit.SPIRST = 1; // SPI Reset, SPI FIFO can resume transmit/receive SpiaRegs.SPIFFTX.bit.SPIFFENA = 1; // SPI FIFO Enable SpiaRegs.SPIFFTX.bit.TXFIFO = 1; // TX FIFO Release from reset mode SpiaRegs.SPIFFTX.bit.TXFFINTCLR = 1; // Clear TXFIFO Interrupt (W1C: Write on to clear) SpiaRegs.SPIFFTX.bit.TXFFIL = 0x00; // Set TX FIFO Interrupt Level to be 0 SpiaRegs.SPIFFRX.bit.RXFIFORESET = 1; // Release Receive FIFO from reset mode SpiaRegs.SPIFFRX.bit.RXFFINTCLR = 1; // Clear SPI FIFO RXFFINTCLR flag (W1C: write one to clear) SpiaRegs.SPIFFRX.bit.RXFFIL = 0x0; // Set RX FIFO Interrupt Level to be 0 SpiaRegs.SPIFFCT.bit.TXDLY = 0x00; // FIFO transmit delay to be zero SpiaRegs.SPICCR.bit.SPISWRESET=1; // Release SPI from reset mode } void SpiTxDat(Uint16 tx) { /*MASTER SEND TIME TO SLAVE*/ GpioDataRegs.GPACLEAR.bit.GPIO19 = 1; SpiaRegs.SPITXBUF = tx; // Load data to SPI Output Buffer while(SpiaRegs.SPIFFRX.bit.RXFFST != 1); // Wait until data is received DataSpiRx = SpiaRegs.SPIRXBUF; // Read received data GpioDataRegs.GPASET.bit.GPIO19 = 1; }

DEVICE #2

void InitSpiFifoSlave() { /*Initializa SPI Slave Mode without FIFO*/ SpiaRegs.SPICCR.bit.SPISWRESET = 0; // Reset SPI SpiaRegs.SPICCR.bit.SPICHAR = 0xF; // Set SPI charater length to be 16-bit (0xF) SpiaRegs.SPICTL.bit.MASTER_SLAVE = 0; // Master->1, Slave->0 SpiaRegs.SPICTL.bit.TALK = 1; // Transmit Enable. Set as 0 will disable TX for next word by set output line HIGH SpiaRegs.SPIBRR = 0x0063; // Set baud rate: 40MHz/(0x63+0x1)=40MHz/100=400bps SpiaRegs.SPIPRI.bit.FREE = 1; // Enable Free Run, continure SPI operation no matter the suspend occurred /*Set SPI FIFO Regs*/ SpiaRegs.SPIFFTX.bit.SPIRST = 1; // SPI Reset, SPI FIFO can resume transmit/receive SpiaRegs.SPIFFTX.bit.SPIFFENA = 1; // SPI FIFO Enable SpiaRegs.SPIFFTX.bit.TXFIFO = 1; // TX FIFO Release from reset mode SpiaRegs.SPIFFTX.bit.TXFFINTCLR = 1; // Clear TXFIFO Interrupt (W1C: Write on to clear) SpiaRegs.SPIFFTX.bit.TXFFIL = 0x00; // Set TX FIFO Interrupt Level to be 0 SpiaRegs.SPIFFRX.bit.RXFIFORESET = 1; // Release Receive FIFO from reset mode SpiaRegs.SPIFFRX.bit.RXFFINTCLR = 1; // Clear SPI FIFO RXFFINTCLR flag (W1C: write one to clear) SpiaRegs.SPIFFRX.bit.RXFFIL = 0x0; // Set RX FIFO Interrupt Level to be 0 SpiaRegs.SPIFFCT.bit.TXDLY = 0x00; // FIFO transmit delay to be zero SpiaRegs.SPICCR.bit.SPISWRESET=1; // Release SPI from reset mode } void SpiRxDat(void) { SpiaRegs.SPITXBUF = 0xF; while(SpiaRegs.SPIFFRX.bit.RXFFST != 1); // Wait until data is received DataSpiRx = SpiaRegs.SPIRXBUF; }

I am not sure which setup is wrong in my code.

"

Thank you very much for your help.

Best regards,