Hello,

I am exploring the possibility of using the CLB to do advanced EPWM tripping (basically, increasing the flexibility of the embedded epwm tripzone submodule).

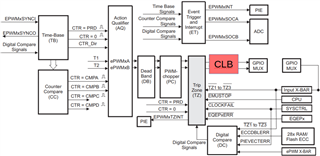

For that, my idea was to do something like in the picture below: the outputs of the Trip Zone submodule would enter in a CLB tile as inputs (toguether with other inputs from the Digital Compare submodule), and then the output of the CLB would intersect the final EPWM that goes to the actual GPIO depending on the inputs and the state of the CLB finite state machines.

For the moment, selecting the input is clear for me (as far as i know). In the SysCfg tool, I simply select the inputs to come from the global mux, and then i select the "EPWM1A/B trip output" signal.

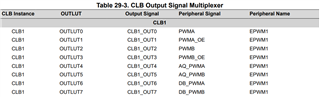

However, for the output is not so clear to me. According to the technical reference manual, these are the possible output intersections with EPWM 1 (for example):

So, my question is: what output should I select so that the output of the CLB overrides the output of the trip zone and goes directly to the GPIO? I am doubting between PWMA and PWMA_OE, but it is not clear what each of them means. What is the difference? Which one should I use?

Thank you and best regards,

Jorge.