Part Number: TMS320F280025

Other Parts Discussed in Thread: SYSCONFIG, C2000WARE

I am using the SCI in an interrupt mode. No FIFO.

When I receive a charachter (8 bits, 9600 baud, no parity, one stop bit) I get an interrupt. In the interrupt routine, I pull the character out of the buffer and put it in my own RXBuf buidling the message. All the while, I look for a <CR> as the termination character so I can set a flag that tells the main routine that there is a message ready. This is a technique I have used for 40 years or so across a wide variety of processors. Those include the 2406 and 28069. Really basic stuff.

If I use a terminal program like Hyper terminal and send my messages one character at a time, all is well. The bytes get put in to my receive buffer, When I hit <CR> the message is decoded and acted upon.

PROBLEM:

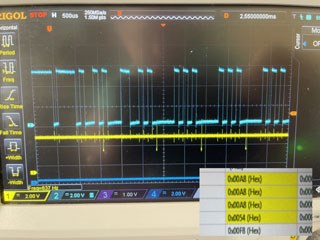

If I use my application (been using it for 20 plus years) which allows me to send the entire message with one click, the interrupts still happen on every charater, but what comes out of the 280025 RXBUF is gibberish. The bytes comeing out do not match what is going in. IT's as though the characters have not actually been fully shifted in to the buffer. Naturally, the bytes coming out of my application come one right after the other but the proper start and stop bits are there so it should NOT be a timing thing.

Any clue as to what the heck is going on?

As always, all brilliant suggestions and dumb ideas welcome...