Hi team,

Here's an issue from the customer may need your help:

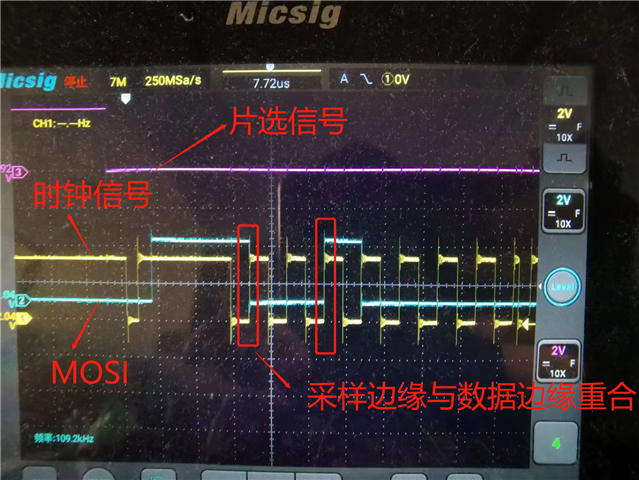

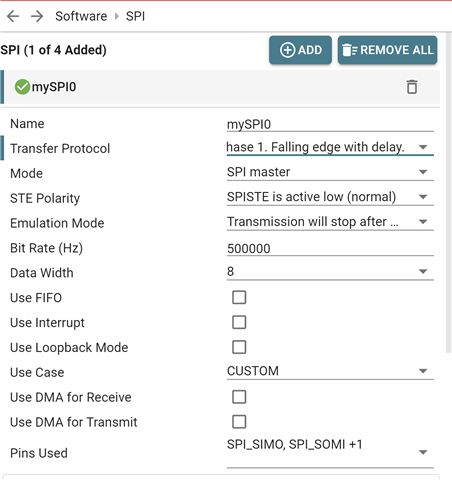

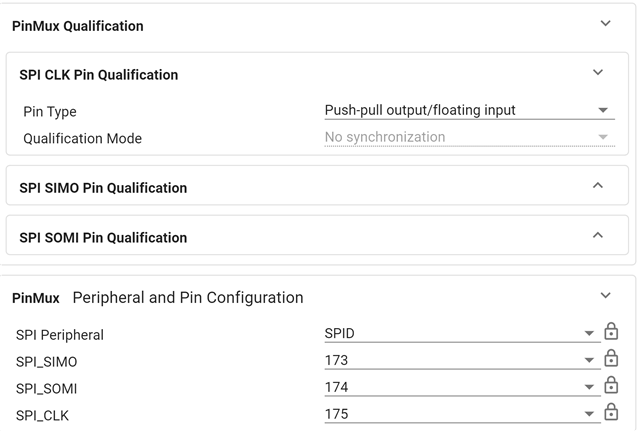

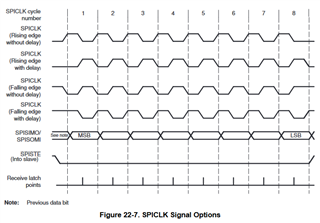

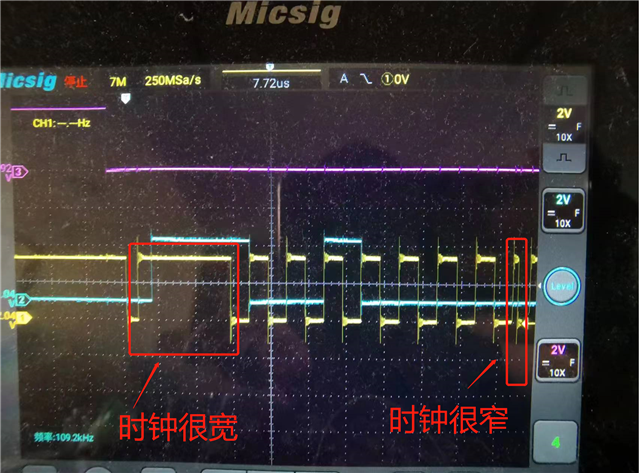

Use the syscfg tool configuration to generate the following SPI initialization code to access the SPI serial flash. When reading the device ID, send a 0x90 command to flash. The measurement waveform is shown in the following figure:

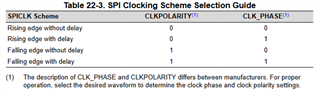

It was found that the waveform clock generated by the DSP chip is essentially aligned with the edges of the MOSI line, causing the device ID to not be read correctly.

So the customer would like to know are there any initialization configurations that can be used to optimize the waveform?

void mySPI0_init(){

SPI_disableModule(mySPI0_BASE);

SPI_setConfig(mySPI0_BASE, DEVICE_LSPCLK_FREQ, SPI_PROT_POL1PHA1,

SPI_MODE_MASTER, 500000, 8);

SPI_disableFIFO(mySPI0_BASE);

SPI_disableLoopback(mySPI0_BASE);

SPI_setEmulationMode(mySPI0_BASE, SPI_EMULATION_STOP_AFTER_TRANSMIT);

SPI_enableModule(mySPI0_BASE);

}

Could you help check this case? Thanks.

Best Regards,

Cherry

(the red blocks represent the wide and narrow clock)

(the red blocks represent the wide and narrow clock)