We've seen that the last comment in

says that it was going to be checked internally, but there was no update.

Could someone at TI please check this topic and give an answer?

Thanks in advance

JPantoja

This thread has been locked.

If you have a related question, please click the "Ask a related question" button in the top right corner. The newly created question will be automatically linked to this question.

We've seen that the last comment in

says that it was going to be checked internally, but there was no update.

Could someone at TI please check this topic and give an answer?

Thanks in advance

JPantoja

Hi Jacobo,

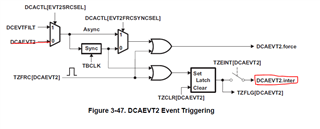

I will take a look at this thread and respond to you by end of day. To my understanding DCAEVT2 can not be configured to be one shot and thus will need a work around. Did the answer that the other Application engineer responded with not work in their application?

Best,

Ryan Ma

Hi Jacobo,

Has the customer tried using DCAEVT2.inter instead of DCAEVT2.force, to generate an interrupt and within that ISR they can set the TZCLR[OST] = 1.

They need to make sure to not select any trip from TZSEL[DCBEVT2] register.

Best,

Ryan Ma