Part Number: TMS320F280049C

Other Parts Discussed in Thread: SYSCONFIG

Dear TI Community.

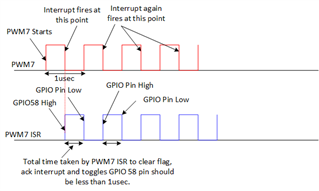

A problem has been boggling me for a couple of days, for which I need your help. I use SYSGONFIG Tool to initialize and program my ePWMs for a 3-phase DAB converter. I have enabled an extra epwm7A on my F280049C to 1usec pulse width (1MHz). I wish to initiate a PWM ISR at a location where the time base counter is equal to CMPA when the counter is going up (PWM generation is achieved in counter UPDOWN mode). In other words, Ideally, the ISR should fire at the middle of the PWM pulse whenever the time base counter is equal to the CPMA value. The ISR asserts the GPIO58 high on entry, clears interrupt flags, acknowledges interrupt, and clears the GPIO58 pin. What I have in mind is something like this.

According to TRM, interrupt latency is 14 sysclock cycles. With my F20049C operating at 100Mhz, the ISR should trigger within 140nsec.

Similarly, the ISR should process the request in less than 1usec and be ready to trigger again upon the next interrupt, which arrives after 1usec. Here is my ISR code

__interrupt void epwm7ISR(void)

{

GPIO_writePin(myGPIO0, 1); // GPIO58 is high

EPWM_clearEventTriggerInterruptFlag(myEPWMTRG_BASE);

//

// Acknowledge this interrupt to receive more interrupts from group 3

//

Interrupt_clearACKGroup(INTERRUPT_ACK_GROUP3);

GPIO_writePin(myGPIO0, 0); // GPIO58 is low

}

Additionally, I have set the GPIO pin configuration as below.

GPIO_setQualificationPeriod(56,1); // 56 for GPIO56 to GPIO63

GPIO_setQualificationMode(58 , GPIO_QUAL_SYNC);

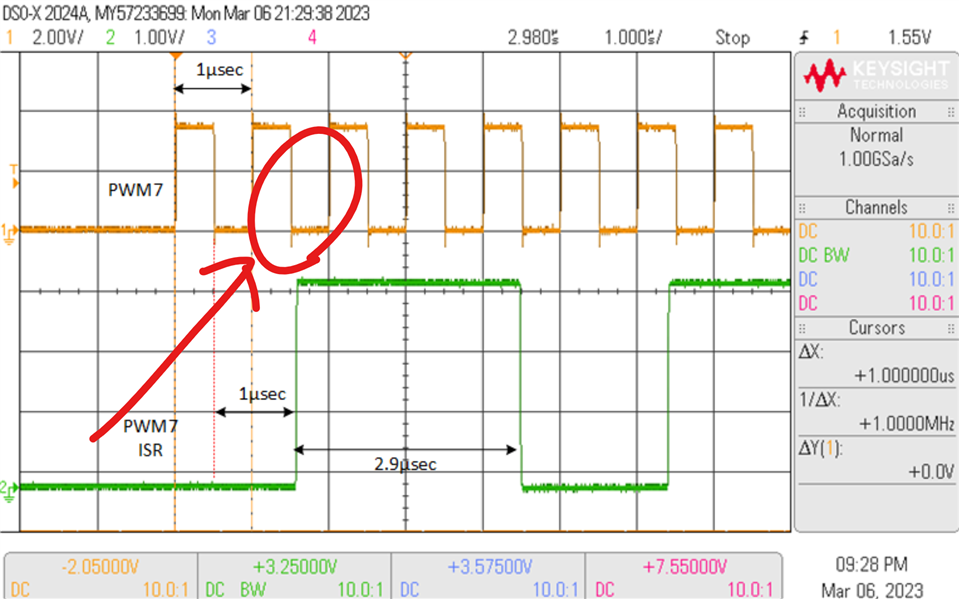

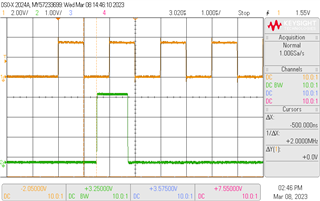

Instead when I try it on the actual hardware this is the best I could achieve.

Here, the interrupt latency is almost 1usec, and the ISR execution time is 2.9usec.

I want to know if it is normal behavior of F280049C operating at 100Mhz. I need a <1usec resolution to read the outputs of CMPSS on the comparator section and be ready to reread those outputs after 1usec. But with this behavior, I cannot get a <1usec reading resolution.

Help anyone.

Regards

Shahamat